MOS tranzistors ir vissvarīgākais elements liela mēroga integrālās shēmas projektēšanā. Šie tranzistori parasti tiek iedalīti divos veidos PMOS un NMOS. NMOS un PMOS tranzistoru kombinācija ir pazīstama kā a CMOS tranzistors . Atšķirīgo loģikas vārti un citām digitālajām loģikas ierīcēm, kas tiek ieviestas, ir jābūt PMOS loģikai. Šī tehnoloģija ir lēta un tai ir laba izturība pret traucējumiem. Šajā rakstā ir apskatīts viens no MOS tranzistoru veidiem, piemēram, PMOS tranzistors.

Kas ir PMOS tranzistors?

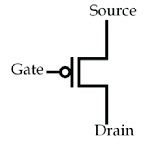

PMOS tranzistors vai P-kanāla metāla oksīda pusvadītājs ir sava veida tranzistors, kurā kanāla vai vārtu reģionā tiek izmantotas p-tipa piedevas. Šis tranzistors ir tieši NMOS tranzistora reverss. Šiem tranzistoriem ir trīs galvenie termināli; avots, vārti un kanalizācija, kur tranzistora avots ir konstruēts ar p-veida substrātu, un drenāžas spaile ir konstruēta ar n-veida substrātu. Šajā tranzistorā lādiņu nesēji kā caurumi ir atbildīgi par strāvas vadīšanu. PMOS tranzistora simboli ir parādīti zemāk.

Kā darbojas PMOS tranzistors?

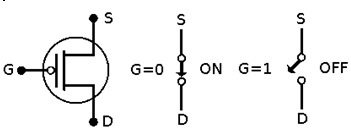

P-tipa tranzistors darbojas diezgan pretējs n-tipa tranzistoram. Šis tranzistors veidos atvērtu ķēdi ikreiz, kad tas saņems nenozīmīgu spriegumu, kas nozīmē, ka nav elektrības plūsmas no vārtu (G) spailes uz avotu (S). Līdzīgi šis tranzistors veido slēgtu ķēdi, kad tas saņem aptuveni 0 voltu spriegumu, kas nozīmē, ka strāva plūst no vārtu (G) spailes uz kanalizāciju (D).

Šis burbulis ir pazīstams arī kā inversijas burbulis. Tātad šī apļa galvenā funkcija ir invertēt ieejas sprieguma vērtību. Ja vārtu spaile nodrošina 1 spriegumu, šis invertors to nomainīs uz nulli un attiecīgi funkcionē ķēdi. Tātad PMOS tranzistora un NMOS tranzistora funkcija ir gluži pretēja. Kad mēs tos apvienosim vienā MOS shēmā, tā kļūs par CMOS (komplementāra metāla oksīda pusvadītāja) ķēdi.

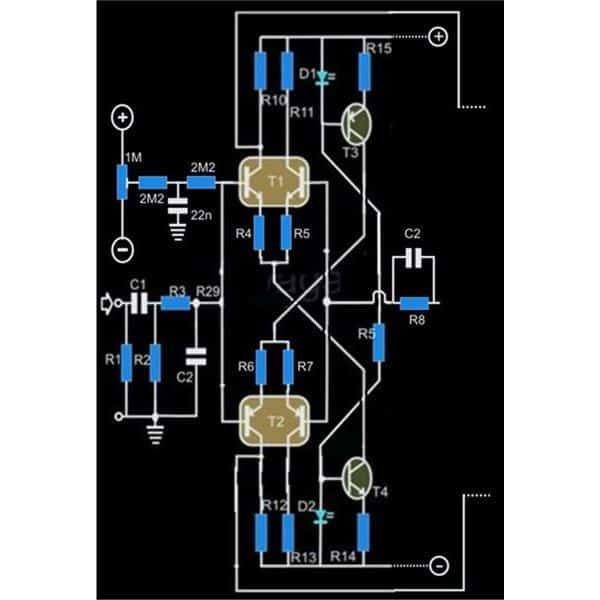

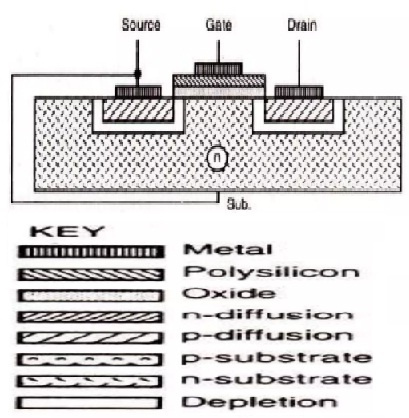

PMOS tranzistora šķērsgriezums

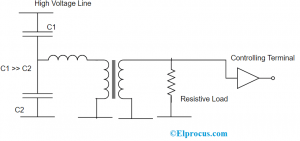

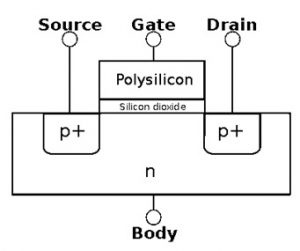

PMOS tranzistora šķērsgriezums ir parādīts zemāk. PMOS tranzistors ir uzbūvēts ar n-veida korpusu, kas ietver divus p-tipa pusvadītāju apgabalus, kas atrodas blakus vārtiem. Šim tranzistoram ir vadības vārti, kā parādīts diagrammā, kas kontrolē elektronu plūsmu starp diviem spailēm, piemēram, avotu un aizplūšanu. pMOS tranzistorā korpuss tiek turēts pie +ve sprieguma. Kad vārtu spaile ir pozitīva, avota un iztukšošanas spailes ir apgrieztas. Kad tas notiek, strāva neplūst, tāpēc tranzistors tiks IZSLĒGTS.

Kad sprieguma padeve pie vārtu spailes ir pazemināta, pozitīvie lādiņu nesēji tiks piesaistīti Si-SiO2 saskarnes apakšai. Ikreiz, kad spriegums kļūst pietiekami zems, kanāls tiks apgriezts un izveido vadošu ceļu no avota spailes uz kanalizāciju, ļaujot plūst strāvai.

Ikreiz, kad šie tranzistori nodarbojas ar digitālo loģiku, parasti ir tikai divas dažādas vērtības, piemēram, 1 un 0 (ON un OFF). Tranzistora pozitīvais spriegums ir pazīstams kā VDD, kas apzīmē loģikas augsto (1) vērtību digitālajās shēmās. VDD sprieguma līmeņi iekšā TTL loģika parasti bija ap 5V. Pašlaik tranzistori faktiski nevar izturēt tik augstu spriegumu, jo tie parasti svārstās no 1,5 V līdz 3,3 V. Zemspriegums bieži tiek saukts par GND vai VSS. Tātad VSS apzīmē loģiku “0”, un tas arī parasti ir iestatīts uz 0 V.

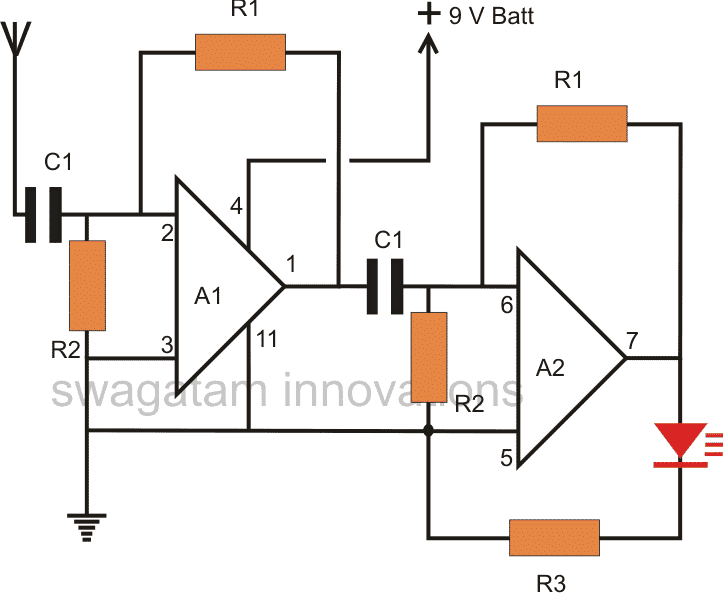

PMOS tranzistora ķēde

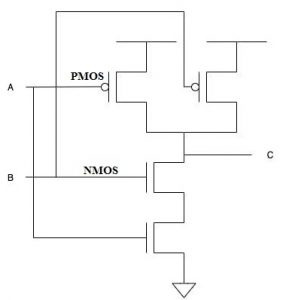

NAND vārtu dizains, izmantojot PMOS tranzistoru un NMOS tranzistoru, ir parādīts zemāk. Parasti NAND vārti digitālajā elektronikā ir loģiski vārti, ko sauc arī par NOT-AND vārtiem. Šo vārtu izvade ir zema (0) tikai tad, ja abas ieejas ir augstas (1) un tās izvade ir UN vārtu papildinājums. Ja kāda no divām ieejām ir LOW (0), tas dod augstus izvades rezultātus.

Zemāk redzamajā loģiskajā shēmā, ja ieeja A ir 0 un B ir 0, pMOS ieeja radīs “1” un nMOS A ieeja radīs “0”. Tātad šie loģiskie vārti ģenerē loģisku “1”, jo tie ir savienoti ar avotu ar slēgtu ķēdi un ir atdalīti no GND caur atvērtu ķēdi.

Ja A ir “0” un B” ir “1”, pMOS ievade ģenerēs “1”, bet NMOS ieeja ģenerēs “0”. Tādējādi šie vārti radīs loģisku, jo tie ir savienoti ar avotu caur slēgtu ķēdi un atdalīti no GND ar atvērtu ķēdi. Ja A ir “1” un B ir “0”, tad pMOS “B” ieeja ģenerēs augstu izvadi (1) un NMOS “B” ieeja ģenerēs tik zemu izvadi (0). Tātad šie loģiskie vārti ģenerēs loģisko 1, jo tie ir savienoti ar avotu caur slēgtu ķēdi un atdalīti no GND ar atvērtu ķēdi.

Ja A ir “1” un B ir “1”, tad “pMOS” ievade radīs nulli, bet nMOS ievade – “1”. Līdz ar to mums vajadzētu pārbaudīt arī pMOS un nMOS B ievadi. PMOS B ieeja ģenerēs “0”, bet nMOS B ievade ģenerēs “1”. Tātad šie loģiskie vārti ģenerēs loģisku “0”, jo tie ir atdalīti no avota ar atvērtu ķēdi un ir savienoti ar GND caur slēgtu ķēdi.

Patiesības tabula

Iepriekš minētās loģiskās shēmas patiesības tabula ir dota zemāk.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

PMOS tranzistora sliekšņa spriegums parasti ir “Vgs”, kas nepieciešams, lai izveidotu kanālu, kas pazīstams kā kanāla inversija. PMOS tranzistorā substrāts un avota spailes ir vienkārši savienotas ar “Vdd”. Ja mēs sākam samazināt spriegumu, atsaucoties uz avota spaili pie vārtu spailes no Vdd līdz vietai, kur pamanāt kanāla inversiju, šajā pozīcijā, analizējot Vgs un avota augstu potenciālu, jūs iegūsit negatīvu vērtību. Tātad, PMOS tranzistoram ir negatīva V. vērtība.

PMOS ražošanas process

Tālāk ir apskatīti PMOS tranzistora izgatavošanas soļi.

1. darbība:

Plāns silīcija vafeles slānis tiek pārveidots par N-veida materiālu, vienkārši leģējot fosfora materiālu.

2. darbība:

Biezs silīcija dioksīda (Sio2) slānis tiek audzēts uz pilnīga p-veida substrāta.

3. darbība:

Tagad virsma ir pārklāta ar fotorezistu virs biezā silīcija dioksīda slāņa.

4. darbība:

Pēc tam šo slāni vienkārši pakļauj UV gaismai caur masku, kas kopā ar tranzistora kanāliem nosaka tos reģionus, kuros jānotiek difūzijai.

5. darbība:

Šie apgabali ir iegravēti kopā ar pamatā esošo silīcija dioksīdu, lai vafeles virsma būtu pakļauta maskas noteiktajam logam.

6. darbība:

Atlikušais fotorezists tiek atdalīts, un plāns Sio2 slānis parasti tiek audzēts 0,1 mikrometru garumā pa visu mikroshēmas virsmu. Pēc tam virs tā tiek uzlikts polisilīcijs, lai izveidotu vārtu struktūru. Fotorezists tiek uzklāts uz visa polisilīcija slāņa un pakļauj UV gaismu caur masku2.

7. darbība:

Difūziju panāk, karsējot vafeles līdz maksimālajai temperatūrai un izlaižot gāzi ar vajadzīgajiem p-veida piemaisījumiem, piemēram, boru.

8. darbība:

Tiek izaudzēts 1 mikrometra biezs silīcija dioksīds un uz tā tiek uzklāts fotorezista materiāls. Atklājiet ultravioleto gaismu ar masku3 uz vēlamajām vārtu, avota un kanalizācijas vietām, kas ir iegravētas, lai veiktu kontakta griezumus.

9. darbība:

Tagad virs tā 1 mikrometra biezuma virsmas ir nogulsnēts metāls vai alumīnijs. Atkal visā metālā tiek izaudzēts fotorezista materiāls, un tas tiek pakļauts UV gaismai caur masku4, kas ir iegravēta, lai izveidotu vajadzīgo starpsavienojumu dizainu. Galīgā PMOS struktūra ir parādīta zemāk.

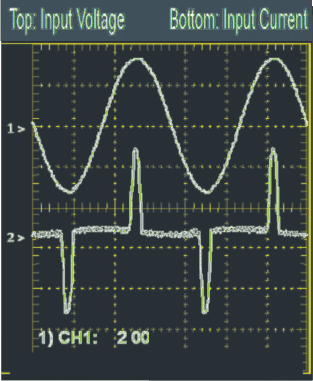

PMOS tranzistora raksturlielumi

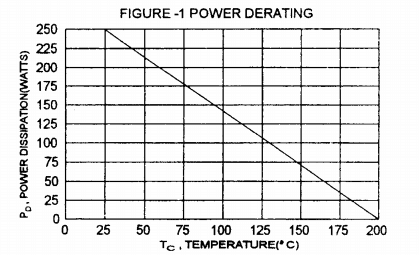

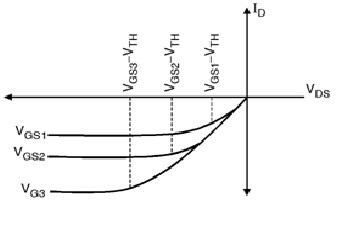

PMOS tranzistora I-V raksturlielumi ir parādīti zemāk. Šie raksturlielumi ir sadalīti divos reģionos, lai iegūtu saistību starp aizplūšanu un avota strāvu (I DS), kā arī tās spaiļu spriegumiem, piemēram, lineāro un piesātinājuma reģionu.

Līnijas apgabalā IDS lineāri palielināsies, kad tiek palielināts VDS (noteces uz avotu spriegums), turpretim piesātinājuma reģionā I DS ir stabils un nav atkarīgs no VDS. Galvenā saistība starp ISD (avota uz iztukšošanas strāvu) un tā spaiļu spriegumiem tiek iegūta ar līdzīgu NMOS tranzistora procedūru. Šajā gadījumā vienīgās izmaiņas būs lādiņu nesēji, kas atrodas inversijas slānī, ir vienkārši caurumi. Kad caurumi pārvietojas no avota uz kanalizāciju, arī strāvas plūsma ir tāda pati.

Tādējādi pašreizējā vienādojumā parādās negatīvā zīme. Turklāt visas ierīces spailēs izmantotās novirzes ir negatīvas. Tātad, PMOS tranzistora ID — VDS raksturlielumi ir parādīti zemāk.

Drenāžas strāvas vienādojums PMOS tranzistoram lineārajā reģionā ir norādīts šādi:

ID = – mp Cox

Tāpat drenāžas strāvas vienādojums PMOS tranzistoram piesātinājuma reģionā ir norādīts kā:

ID = – mp Cox (VSG – | V TH |p )^2

Kur “mp” ir cauruma mobilitāte un “|VTH| p’ ir PMOS tranzistora sliekšņa spriegums.

Iepriekš minētajā vienādojumā negatīvā zīme norāda, ka ID ( drenāžas strāva ) plūst no notekas (D) uz avotu (S), bet caurumi plūst pretējā virzienā. Ja cauruma mobilitāte ir zema salīdzinājumā ar elektronu mobilitāti, PMOS tranzistori cieš no zemas strāvas piedziņas iespējas.

Tādējādi tas viss ir par PMOS tranzistora vai p-tipa mos tranzistora pārskatu - izgatavošanu, ķēdi un tā darbību. PMOS ir paredzēti tranzistori ar p-avotu, n-substrātu un kanalizāciju. PMOS lādiņu nesēji ir caurumi. Šis tranzistors vada, kad vārtu spailē tiek pielikts zems spriegums. Ierīces, kuru pamatā ir PMOS, ir mazāk pakļautas traucējumiem, salīdzinot ar NMOS ierīcēm. Šos tranzistorus var izmantot kā sprieguma kontrolētus rezistorus, aktīvās slodzes, strāvas spoguļus, trans-impedances pastiprinātājus, kā arī izmantot slēdžos un sprieguma pastiprinātājos. Šeit ir jautājums jums, kas ir NMOS tranzistors?