Dažādu veidu digitālās sistēmas tiek veidotas no ļoti dažiem tīkla pamatkonfigurāciju veidiem, piemēram, AND vārti, NAND vārti, vārti utt. Šīs elementārās shēmas tiek izmantotas atkal un atkal dažādās topoloģiskajās kombinācijās. Papildus loģikas veikšanai digitālajām sistēmām ir jāuzglabā arī bināri skaitļi. Šīm atmiņas šūnām, kas pazīstamas arī kā FLIP-FLOP ’ ir paredzēti. Lai veiktu dažas funkcijas, piemēram, bināro pievienošanu. Tādējādi, lai veiktu šādas funkcijas, to kombinācijas loģikas vārti un FLIP-FLOP ir izstrādāti, izmantojot vienas mikroshēmas IC. Šie IC veido digitālo sistēmu praktiskos elementus. Viens no šādiem blokiem, ko izmanto binārā pievienošanai, ir Carry Look-forward Adder.

Kas ir Carry Look-forward papildinātājs?

Digitālajā datorā jābūt ķēdēm, ar kurām var veikt tādas aritmētiskas darbības kā saskaitīšana, atņemšana, reizināšana un dalīšana. Starp tām saskaitīšana un atņemšana ir pamatdarbības, savukārt reizināšana un dalīšana ir attiecīgi atkārtota saskaitīšana un atņemšana.

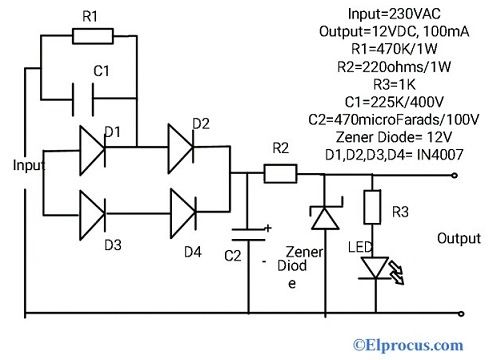

Lai veiktu šīs darbības, ‘papildinātāju shēmas’ tiek realizētas, izmantojot pamata loģiskos vārtus. Papildinātāju shēmas ir attīstījušies kā Puspapildinātājs, Pilnpapildinātājs, Ripple-carry papildinātājs un Carry Look-forward papildinātājs.

Starp šiem Carry Look-forward Adder ir ātrāka papildinātāja ķēde. Tas samazina izplatīšanās kavēšanos, kas rodas pievienošanas laikā, izmantojot sarežģītākas aparatūras shēmas. Tas ir izveidots, pārveidojot pulsācijas pārnēsāšanas Adder ķēdi tā, lai papildinātāja pārneses loģika tiktu mainīta par divu līmeņu loģiku.

4 bitu pārnesumkārbas papildinātājs

Paralēli summētājiem katra pilnā papildinātāja izejas vērtība tiek dota kā pārneses ievads nākamajam augstākās kārtas stāvoklim. Tādējādi šiem summētājiem nav iespējams radīt jebkura stāvokļa pārneses un summēšanas rezultātus, ja vien šai valstij nav pieejama pārnešanas ievade.

Tātad, lai notiktu aprēķins, ķēdei jāgaida, līdz pārnēsāšanas bits izplatās visos stāvokļos. Tas izraisa ķēdes pārnešanas aizkavēšanos.

4 bitu Ripple-Carry-Adder

Apsveriet iepriekš minēto 4 bitu pulsācijas nesēju papildināšanas shēmu. Šeit summu S3 var uzrādīt, tiklīdz tiek doti ievadi A3 un B3. Bet pārnēsāšanu C3 nevar aprēķināt, kamēr nav izmantots pārneses bits C2, savukārt C2 ir atkarīgs no C1. Tāpēc, lai iegūtu galīgos līdzsvara stāvokļa rezultātus, pārnēsāšanai ir jāpāriet cauri visiem stāvokļiem. Tas palielina ķēdes pārnēsāšanas izplatīšanās kavēšanos.

Skaitītāja izplatīšanās aizkave tiek aprēķināta kā “katra vārta izplatīšanās aizture reizina ķēdes posmu skaitu”. Lai aprēķinātu lielu skaitu bitu, ir jāpievieno vairāk posmu, kas aizkavē daudz vairāk. Tādējādi, lai atrisinātu šo situāciju, tika ieviests Carry Look-forward Adder.

Lai izprastu Carry Look-forward papildinātāja darbību, turpmāk aprakstīts 4 bitu Carry Look-forward Adder.

4 bitu pārnēsāšanas-skatīšanās uz priekšu-papildinātāja-loģikas-diagramma

Šajā papildinātājā pārnēsāšanas ievade jebkurā papildinātāja posmā ir neatkarīga no nesošajiem bitiem, kas ģenerēti neatkarīgajos posmos. Šeit jebkura posma izeja ir atkarīga tikai no bitiem, kas pievienoti iepriekšējos posmos, un sākuma posmā paredzētajām pārnēsāšanas ieejām. Tādējādi ķēdei nevienā posmā nav jāgaida pārnēsājamo bitu ģenerēšana no iepriekšējā posma, un pārnēsāšanas bitu var novērtēt jebkurā laika posmā.

Patiesības pārnesumkārbas papildinātāja tabula

Lai iegūtu šī papildinātāja patiesības tabulu, tiek ieviesti divi jauni termini - Pārnēsāt, ģenerēt un Pārnēsāt. Pārnēsāšanas ģenerators Gi = 1 ikreiz, kad rodas ģenerācija Ci + 1. Tas ir atkarīgs no Ai un Bi ievadiem. Gi ir 1, ja Ai un Bi ir 1. Tādējādi Gi tiek aprēķināts kā Gi = Ai. Bi.

Pārnēsātais pavairotais Pi ir saistīts ar pārnešanas izplatīšanos no Ci uz Ci + 1. To aprēķina kā Pi = Ai ⊕ Bi. Šī papildinātāja patiesības tabulu var iegūt, modificējot pilna papildinātāja patiesības tabulu.

Izmantojot Gi un Pi terminus, summa Si un Carry Ci + 1 ir doti šādi:

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Tāpēc pārneses bitus C1, C2, C3 un C4 var aprēķināt kā

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0). P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1). P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

To var novērot no vienādojumiem, kas nes Ci + 1, ir atkarīgs tikai no pārneses C0, nevis no starpnesošajiem bitiem.

Carry-Look-forward-Adder-Patiesības tabula

Ķēdes shēma

Iepriekš minētie vienādojumi tiek īstenoti, izmantojot divu līmeņu kombinētās shēmas kopā ar AND, OR vārtiem, kur tiek pieņemts, ka vārtiem ir vairākas ieejas.

Carry-Output-Generation-Circuit-of-Carry-Look-priekšu-papildinātājs

Carry Look-forward Adder ķēde no 4 bitiem ir dota zemāk.

4 bitu pārnēsāšanas-skatīšanās uz priekšu-papildinātāja shēmas diagramma

8 bitu un 16 bitu Carry Look-forward papildinātāju shēmas var izveidot, 4-bitu papildinātāju ķēdi kaskādējot ar pārneses loģiku.

Carry Look-forward Adder priekšrocības

Šajā papildinātājā tiek samazināta izplatīšanās kavēšanās. Pārnēsāšanas jauda jebkurā posmā ir atkarīga tikai no sākuma posma sākotnējā pārneses bita. Izmantojot šo papildinājumu, ir iespējams aprēķināt starpposma rezultātus. Šis papildinātājs ir ātrākais skaitļošanai izmantotais papildinātājs.

Pieteikumi

Ātrgaitas Carry Look-forward papildinātāji tiek izmantoti kā ieviesti kā IC. Tādējādi papildinātāju ir viegli ievietot ķēdēs. Apvienojot divus vai vairākus papildinātājus, var viegli veikt aprēķinus par lielākiem būla funkcijām. Šeit arī vārtu skaita pieaugums ir mērens, ja tos izmanto lielākiem bitiem.

Šim papildinātājam ir kompromiss starp laukumu un ātrumu. Ja to izmanto lielāku bitu aprēķiniem, tas nodrošina lielu ātrumu, bet tiek palielināta arī ķēdes sarežģītība, tādējādi palielinot ķēdes aizņemto laukumu. Šis papildinātājs parasti tiek ieviests kā 4 bitu moduļi, kas tiek apvienoti kaskādē, ja tos izmanto augstākiem aprēķiniem. Šis papildinātājs ir dārgāks, salīdzinot ar citiem pievienotājiem.

Būla skaitļošanai datoros papildinātāji tiek regulāri izmantoti. Čārlzs Bebeds ieviesa mehānismu, kā paredzēt datora pārnēsāšanas bitu, lai samazinātu pulsācijas pārnēsātāji . Projektējot sistēmu, aprēķina ātrums ir augstākais dizainera izšķirošais faktors. Džeralds B. Rozenbergers 1957. gadā patentēja moderno Binary Carry Look-forward Adder. Pamatojoties uz vārtu aiztures un simulācijas analīzi, tiek veikti eksperimenti, lai modificētu šī papildinātāja ķēdi, lai padarītu to vēl ātrāku. Kāda ir pavairošanas aizkava n-bitu pārredzama papildinātāja gadījumā, ja katras vārtu aizkave ir 20?

Attēlu kredīts