JTAG (Joint Test Action Group) ir vispāratzīts IEEE 1149.1 standarts, kas tika izstrādāts 1980. gadā, lai atrisinātu ražošanas problēmas, kas radās elektroniskajās platēs vai iespiedshēmu plates . Šī tehnoloģija tiek izmantota, lai nodrošinātu pietiekamu testa piekļuvi katrai sarežģītajai platei, kad testa piekļuve samazinās. Tādējādi tika uzsākta robežu skenēšanas tehnoloģija & JTAG standarts vai JTAG specifikācija ir izveidota. Elektronikas sarežģītība ar katru dienu pieaug, tāpēc JTAG specifikācija ir kļuvusi par pieņemto testa formātu, lai pārbaudītu sarežģītas un kompaktas elektronikas vienības. Šajā rakstā ir apskatīts pārskats par a JTAG protokols – darbs ar aplikācijām.

Kas ir JTAG?

Nosaukums, kas tiek piešķirts IEEE 1149.1 standarta pārbaudes piekļuves portam, kā arī robežu skenēšanas arhitektūrai, ir pazīstams kā JTAG (Apvienotā testa darbības grupa). Šī robežu skenēšanas arhitektūra galvenokārt tiek izmantota datorā procesori jo Intel izlaida pirmo procesoru ar JTAG. Šis IEEE standarts vienkārši nosaka, kā tiek pārbaudīta datora shēma, lai pārliecinātos, vai tas darbojas pareizi pēc ražošanas procedūras. Uz shēmas plates tiek veikti testi, lai pārbaudītu lodēšanas savienojumus.

Apvienotā testa darbības grupa testētājiem ar katru IC spilventiņu nodrošina kontaktu skatu, kas palīdz identificēt shēmas plates defektus. Kad šis protokols ir savienots ar mikroshēmu, tas var pievienot mikroshēmai zondi, ļaujot izstrādātājam kontrolēt mikroshēmu, kā arī tās savienojumus ar citām mikroshēmām. Izstrādātāji var izmantot arī saskarni ar kopīgās pārbaudes darbības grupu, lai kopētu programmaparatūru elektroniskās ierīces nemainīgā atmiņā.

Konfigurācija/Pin Out

Apvienotajā testa darbības grupā ir 20 tapas, kur katra tapa un tās funkcija ir aplūkota turpmāk.

Pin1 (VTref): Šī ir mērķa atsauces sprieguma tapa, ko izmanto, lai izveidotu savienojumu ar mērķa galveno barošanas avotu, kas svārstās no 1,5 līdz 5,0 VDC.

Pin2 (Vsupply): Šis ir mērķa barošanas spriegums, kas tiek izmantots, lai pievienotu mērķa 1,5 V līdz 5, 0 V līdzstrāvas galveno sprieguma padevi.

Pin3 (nTRST): Šī ir testa atiestatīšanas tapa, ko izmanto, lai atiestatītu TAP kontrollera stāvokļa mašīnu.

Spraudītes (4, 6, 8, 10, 12, 14, 16, 18 un 20): Tās ir izplatītas GND tapas.

Pin5 (TDI): Šie ir testa dati tapā. Šie dati tiek pārvietoti uz mērķa ierīci. Šī tapa ir jāizvelk uz augšu noteiktā stāvoklī uz mērķa dēļa.

Pin7 (TMS): Šī ir testa režīma stāvokļa tapa, kas tiek izvilkta, lai noteiktu nākamo TAP kontrollera stāvokļa mašīnas stāvokli.

Pin9 (TCK): Šī ir testa pulksteņa tapa, kas sinhronizē iekšējā stāvokļa mašīnas darbības TAP kontrollerī.

Pin11 (RTCK): Šī ir ievades atgriešanas TCK tapa, kas tiek izmantota ierīcēs, kas atbalsta adaptīvo pulksteni.

Pin13 (TDO): Šī ir testa datu izvades tapa, tāpēc dati tiek pārvietoti no mērķa ierīces uz Flyswatter.

Pin15 (nSRST): Šī ir mērķa sistēmas atiestatīšanas tapa, kas ir savienota ar mērķa galveno atiestatīšanas signālu.

17. un 19. tapas (NC): Tās nav savienotas tapas.

JTAG darbojas

JTAG sākotnēji tiek izmantots robežu testēšanai. Šeit ir vienkārša iespiedshēmas plate, kas ietver divus IC, piemēram, CPU un FPGA . Tipiskā panelī var būt daudz IC. Parasti IC ietver daudzas tapas, kas ir savienotas kopā ar daudziem savienojumiem. Šeit nākamajā diagrammā ir parādīti tikai četri savienojumi.

Tātad, ja jūs projektējat daudzas plates, kur katrai platei ir tūkstošiem savienojumu. Tajā ir daži slikti dēļi. Tāpēc mums ir jāpārbauda, kura plate darbojas un kura nedarbojas. Šim nolūkam tika izveidota Apvienotā pārbaudes rīcības grupa.

Šis protokols var izmantot visu mikroshēmu vadības tapas, bet nākamajā diagrammā Apvienotā testa darbības grupa veiks visas CPU izejas tapas un visas FPGA ievades tapas. Pēc tam, pārsūtot kādu datu apjomu no CPU tapām un nolasot kontaktu vērtības no FPGA, JTAG paziņo, ka PCB plates savienojumi ir labi.

Faktiski Apvienotajā testa rīcības grupā ir četri loģiskie signāli TDI, TDO, TMS un TCK. Un šie signāli ir jāsavieno noteiktā veidā. Sākumā TMS un TCK ir savienoti paralēli visiem JTAG IC.

Pēc tam gan TDI, gan TDO ir savienoti, lai izveidotu ķēdi. Kā jūs varat novērot, katrā ar JTAG saderīgo IC ir 4 kontakti, kas tiek izmantoti JTAG, kur 3 kontakti ir ieejas un 4. kontaktdakša tiek izvadīta. Piektā tapa, piemēram, TRST, nav obligāta. Parasti JTAG tapas netiek koplietotas citiem mērķiem.

Izmantojot Apvienotās pārbaudes darbības grupu, visi IC izmanto robežpārbaudi, kuras sākotnējo iemeslu izveido JTAG. Pašlaik šī protokola izmantošana ir paplašināta, lai atļautu dažādas lietas, piemēram, FPGA konfigurēšanu, un pēc tam JTAG tiek izmantots FPGA kodolā atkļūdošanas nolūkos.

JTAG arhitektūra

JTAG arhitektūra ir parādīta zemāk. Šajā arhitektūrā visi signāli starp ierīces galveno loģiku un tapām tiek pārtraukti, izmantojot seriālo skenēšanas ceļu, ko sauc par BSR vai robežu skenēšanas reģistru. Šis BSR ietver dažādas robežu skenēšanas “šūnas”. Parasti šīs robežu skenēšanas šūnas nav redzamas, taču tās var izmantot, lai testa režīmā iestatītu vai nolasītu vērtības no ierīces tapām.

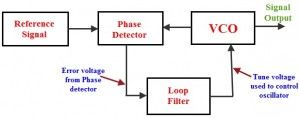

JTAG saskarne, ko sauc par TAP vai Test Access Port, izmanto dažādus signālus, lai atbalstītu robežu skenēšanas darbību, piemēram, TCK, TMS, TDI, TDO un TRST.

- TCK vai testa pulksteņa signāls vienkārši sinhronizē stāvokļa mašīnas iekšējās darbības.

- TMS vai Test Mode Select signāla paraugs tiek ņemts testa pulksteņa signāla pieaugošajā malā, lai noteiktu nākamo stāvokli.

- TDI vai testa datu ievades signāls norāda pārbīdītos datus testa ierīcē, citādi programmēšanas loģika. Kad iekšējā stāvokļa iekārta ir pareizajā stāvoklī, tā tiek ņemta no TCK pieaugošās malas.

- TDO vai testa datu izvades signāls apzīmē testa ierīces pārbīdītos datus, citādi programmēšanas loģika. Kad iekšējā stāvokļa iekārta ir pareizajā stāvoklī, tā ir derīga TCK dilstošajā malā

- TRST vai Test Reset ir izvēles tapa, ko izmanto, lai atiestatītu TAP kontrollera stāvokļa mašīnu.

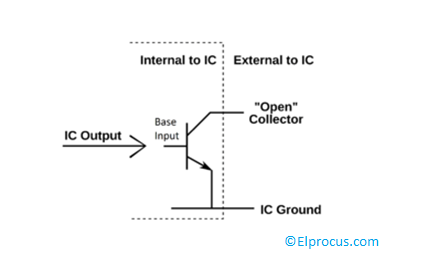

TAP kontrolieris

Testa piekļuves punkts JTAG arhitektūrā sastāv no TAP kontrollera, instrukciju reģistra un testa datu reģistriem. Šis kontrolieris ietver testēšanas stāvokļa mašīnu, kas ir atbildīga par TMS un TCK signālu nolasīšanu. Šeit datu i/p kontakts tiek vienkārši izmantots, lai ielādētu datus robežšūnās starp IC kodolu un fiziskajām tapām, kā arī ielādētu datus vienā no datu reģistriem vai instrukciju reģistrā. Datu o/p tapa tiek izmantota datu nolasīšanai no reģistriem vai robežšūnām.

TAP kontrollera stāvokļa mašīnu kontrolē TMS, un to nosaka TCK. Stāvokļa mašīna izmanto divus ceļus, lai apzīmētu divus dažādus režīmus, piemēram, instrukciju režīmu un datu režīmu.

Reģistri

Robežu skenēšanas ietvaros ir pieejami divu veidu reģistri. Katrā saderīgā ierīcē ir vismaz divi vai vairāk datu reģistri un viens instrukciju reģistrs.

Instrukciju reģistrs

Instrukciju reģistrs tiek izmantots, lai saglabātu pašreizējo instrukciju. Tāpēc TAP kontrolieris izmanto tā datus, lai izlemtu, ko izpildīt ar iegūtajiem signāliem. Visbiežāk instrukciju reģistra dati apraksta, kuram no datu reģistriem ir jānodod signāli.

Datu reģistri

Datu reģistri ir pieejami trīs veidos: BSR (Robežu skenēšanas reģistrs), BYPASS un ID KODU reģistrs. Un arī citi datu reģistri var būt, taču tie nav nepieciešami kā JTAG standarta elements.

Robežu skenēšanas reģistrs (BSR)

BSR ir galvenais testēšanas datu reģistrs, ko izmanto, lai pārsūtītu datus no ierīces I/O tapām un uz tām.

APbrauciens

Apvedceļš ir viena bita reģistrs, ko izmanto, lai nodotu datus no TDI — TDO. Tādējādi tas ļauj pārbaudīt papildu ierīces ķēdē ar minimālu pieskaitāmo slodzi.

ID KODI

Šāda veida datu reģistrs ietver ID kodu, kā arī ierīces versijas numuru. Tādējādi šie dati ļauj ierīci savienot ar tās BSDL (Boundary Scan Description Language) failu. Šajā failā bija iekļauta ierīces robežu skenēšanas konfigurācijas informācija.

JTAG darbība sākotnēji ir tāda, ka tiek izvēlēts instrukciju režīms, kurā viens no šī režīma stāvokļiem “ceļš” ļauj operatoram veikt pulksteni TDI norādījumā. Pēc tam stāvokļa mašīna attīstās, līdz pārkārtojas. Nākamais solis lielākajai daļai norādījumu ir datu režīma izvēle. Tātad šajā režīmā dati tiek ielādēti, izmantojot TDI, lai nolasītu no TDO. TDI un TDO datu ceļi tiks sakārtoti saskaņā ar instrukciju, kas ir iestatīta. Kad lasīšanas/rakstīšanas darbība ir pabeigta, stāvokļa mašīna atkal pāriet uz atiestatīšanas stāvokli.

Atšķirība starp JTAG un UART

Atšķirība starp JTAG un UART ir šāda.

| JTAG |

UART |

| Termins “JTAG” apzīmē Apvienotās pārbaudes darbības grupu. | Termiņš ' UART ” apzīmē universālo asinhrono uztvērēju/raidītāju. |

| Tas ir sinhrons interfeiss, kas izmanto iebūvētu aparatūru zibspuldzes programmēšanai . | UART ir asinhrona saskarne, kas izmanto sāknēšanas ielādētāju, kas darbojas atmiņā. |

| Tas ir testa portu kopums, ko izmanto atkļūdošanai, bet var izmantot arī programmaparatūras programmēšanai (kas parasti tiek darīts).

|

UART ir mikroshēmas veids, kas kontrolē sakarus uz ierīci un no tās, piemēram, mikrokontrolleri, ROM, RAM utt. Lielākoties tas ir seriālais savienojums, kas ļauj mums sazināties ar ierīci. |

| Tie ir pieejami četru veidu TDI, TDO, TCK, TMS un TRST. | Tie ir pieejami divu veidu dump UART un FIFO UART. |

| Joint Test Action Group ir seriālā programmēšana vai datu piekļuves protokols, ko izmanto mikrokontrolleru un saistīto ierīču saskarnē. | UART ir viena veida mikroshēmas, citādi mikrokontrollera apakškomponents, ko izmanto, lai nodrošinātu aparatūru asinhronas sērijas straumes, piemēram, RS-232/RS-485, ģenerēšanai. |

| JTAG komponenti ir procesori, FPGA, CPLD , utt. | UART komponenti ir CLK ģenerators, I/O maiņu reģistri, pārraides vai saņemšanas buferi, sistēmas datu kopnes buferis, lasīšanas vai rakstīšanas vadības loģika utt. |

JTAG protokola analizators

JTAG protokola analizators, piemēram, PGY-JTAG-EX-PD, ir viena veida protokolu analizators, kas ietver dažas funkcijas saziņas uztveršanai un atkļūdošanai starp resursdatoru un testējamo dizainu. Šis analizatora veids ir vadošais instruments, kas ļauj testēšanas un projektēšanas inženieriem pārbaudīt konkrētus JTAG dizainus tā specifikācijām, sakārtojot PGY-JTAG-EX-PD, piemēram, Master vai Slave, lai ģenerētu JTAG trafiku un dekodētu JTAG paketes. Apvienotās pārbaudes rīcības grupas protokols.

Iespējas

JTAG protokola analizatora funkcijas ir šādas.

- Tā atbalsta līdz 25MH JTAG frekvencēm.

- Tas vienlaikus ģenerē JTAG trafiku un protokola atšifrēšanu kopnei.

- Tam ir JTAG Master iespēja.

- Mainīgs JTAG datu ātrums un darba cikls.

- Lietotāja definētas TDI un TCK aizkaves.

- Resursdatora USB 2.0 vai 3.0 interfeiss.

- Kļūdu analīze protokola atkodēšanas ietvaros

- Protokola dekodētā kopnes laika diagramma.

- Nepārtraukta protokola datu straumēšana uz saimniekdatoru, lai nodrošinātu lielu buferi.

- Protokola darbību saraksts.

- Dažādos ātrumos var uzrakstīt vingrinājumu skriptu vairāku datu kadru ģenerēšanas apvienošanai.

Laika diagramma

The JTAG laika diagramma protokols ir parādīts zemāk. Nākamajā diagrammā TDO tapa paliek augstas pretestības stāvoklī, izņemot Shift-IR/shift-DR kontrollera stāvokli.

Shift-IR un Shift-DR kontrollera apstākļos TDO tapa tiek atjaunināta TCK dilstošajā malā, izmantojot Target, un paraugs tiek ņemts no TCK pieaugošās malas, izmantojot Host.

Gan TDI, gan TMS tapas tiek vienkārši atlasītas TCK augošajā malā, izmantojot Target. Atjaunināts dilstošā malā, pretējā gadījumā TCK caur resursdatoru.

Lietojumprogrammas

The JTAG lietojumprogrammas iekļaujiet tālāk norādīto.

- Joint Test Action Group bieži tiek izmantota procesoros, lai nodrošinātu piekļuves tiesības to emulācijas vai atkļūdošanas funkcijās.

- Visi CPLD un FPGA izmanto to kā saskarni, lai nodrošinātu piekļuvi savām programmēšanas funkcijām.

- To izmanto PCB testēšanai bez fiziskas piekļuves

- To izmanto dēļu līmeņa ražošanas testiem.

Tādējādi tas viss ir par JTAG pārskats – tapu konfigurācija, darbs ar aplikācijām. Nozares standarts JTAG tiek izmantots dizaina pārbaudei, kā arī PCB testēšanai pēc ražošanas. Šeit ir jautājums jums, JTAG nozīmē?