Ikdienas dzīvē mēs bieži sazināmies ar citiem, izmantojot dažādus veidus sakaru sistēmas . Šo sakaru sistēmu var klasificēt dažādos veidos, piemēram, radiosakaru sistēmā, telekomunikāciju sistēmā, Bezvadu sakaru sistēma , Optiskā sakaru sistēma utt. Lai visas šīs sakaru sistēmas darbotos efektīvi, mums ir nepieciešamas dažas vadības sistēmas, piemēram, fāzes bloķēta cilpa, kooperatīva vadība, tīkla vadība un tā tālāk.

Kas ir fāzes bloķēta cilpa (PLL)?

Fāzes bloķēta cilpa tiek izmantota kā vadības sistēma, lai kontrolētu dažādas darbības daudzās sakaru sistēmās, datoros un daudzās elektroniskas lietojumprogrammas . To izmanto, lai ģenerētu izejas signālu, kuram ir fāze, kas saistīta ar ieejas signāla fāzi.

Pastāv dažādi PLL veidi, piemēram, Analog vai Linear PLL, Digital PLL, Software PLL, Neuronal PLL un visi digitālie PLL.

Fāzes bloķēta cilpa darbība

Sakaru sistēmās PLL darbību var izskaidrot, apsverot analogās un digitālās sistēmas .

Analogā fāzes bloķētā cilpa sakaru sistēmās

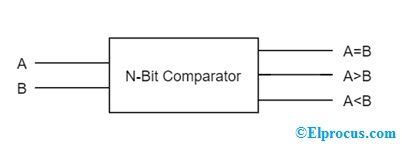

Būtībā PLL ir servo cilpas forma, un pamata PLL sastāv no trim galvenajiem elementiem, proti, fāžu salīdzinātāja / detektora, cilpas filtra un sprieguma kontrolēts oscilators .

Fāzes bloķēta cilpa

Galvenais PPL darbības jēdziens ir divu signālu fāžu salīdzinājums (parasti tiek salīdzinātas ieejas un izejas signāla fāzes). Tādējādi fāzes starpību starp ieejas un izejas signālu var izmantot, lai kontrolētu cilpas frekvenci. Kaut arī matemātiskā analīze ir ļoti sarežģīta, bet PLL darbība ir ļoti vienkārša.

Daudzās sakaru sistēmās PLL tiek izmantots dažādiem mērķiem:

- Lai sekotu fāzei vai frekvences modulācija , to izmanto kā Demodulatoru.

- Lai izsekotu vai sinhronizētu abus signālus ar dažādām frekvencēm.

- Lai noņemtu lielus trokšņus no sīkiem signāliem.

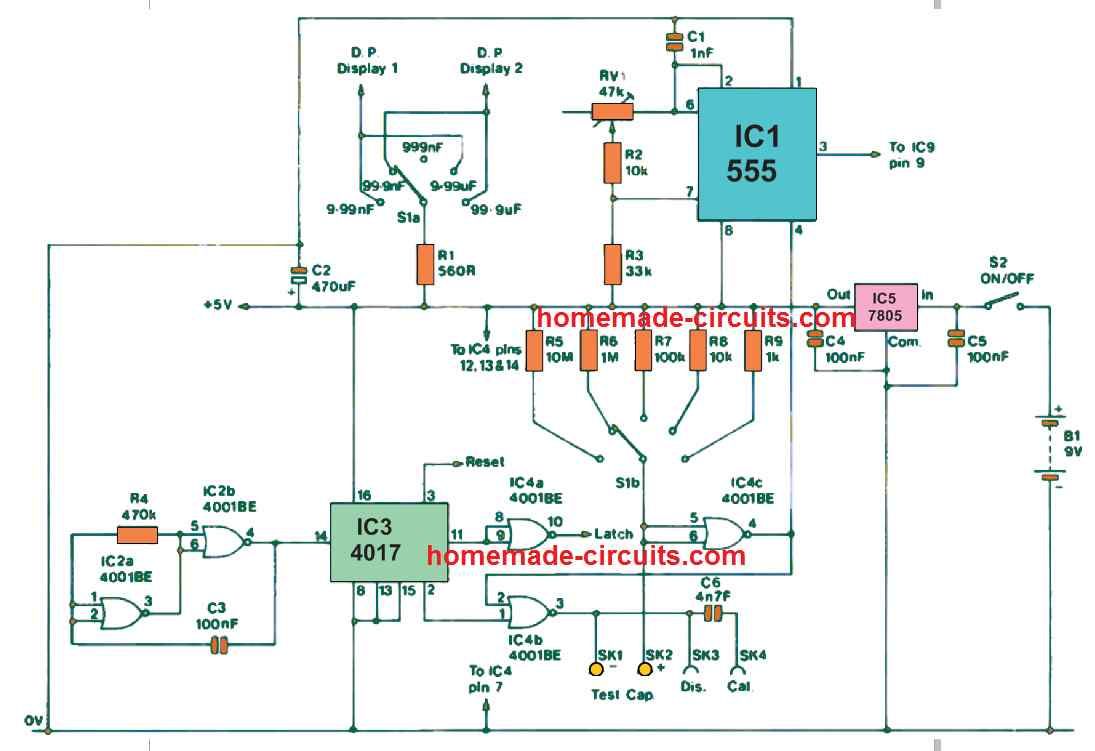

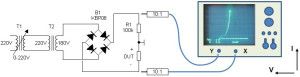

Zemāk redzamajā attēlā parādīts pamata PLL, kas sastāv no fāzes detektora, sprieguma kontrolēta oscilatora (VCO), cilpas filtra.

PLL sprieguma kontrolētais oscilators rada signālu, un šis signāls no VCO tiek ievadīts fāzes detektoram. Fāzes detektors salīdzina šo signālu ar atsauces signālu un tādējādi rada kļūdas spriegumu vai starpības spriegumu. Šis fāzes detektora kļūdas signāls tiek padots zemfrekvences filtram, lai noņemtu signāla augstfrekvences elementus, ja tādi ir, un lai kontrolētu daudzas cilpas īpašības. Tad cilpas filtra izeja tiek padota, lai nodrošinātu sprieguma kontrolētā oscilatora vadības spailes regulēšanas spriegumu.

Tiek uztverta šī regulēšanas sprieguma izmaiņas, lai samazinātu fāžu starpību starp diviem signāliem (ieejas un izejas) un tādējādi starp tiem esošo frekvenci. Sākotnēji PLL netiek bloķēts, un kļūdas spriegums velk VCO frekvenci uz atsauces punktu, līdz kļūdu vairs nevar samazināt un pēc tam cilpa tiek bloķēta.

Faktiskā kļūda starp diviem signāliem (ieeja un izeja) tiek samazināta līdz ļoti mazam līmenim izmantojot pastiprinātāju starp sprieguma kontrolētu oscilatoru un fāzes detektoru. Ja PLL ir bloķēts, rodas stabila stāvokļa kļūdas spriegums. Šis līdzsvara stāvokļa kļūdas spriegums norāda, ka starp atskaites signālu un VCO nav fāzes starpības izmaiņu. Tādējādi mēs varam teikt, ka divu signālu (ieejas un izejas signālu) frekvence ir tieši vienāda.

Digitālā fāzes bloķētā cilpa sakaru sistēmās

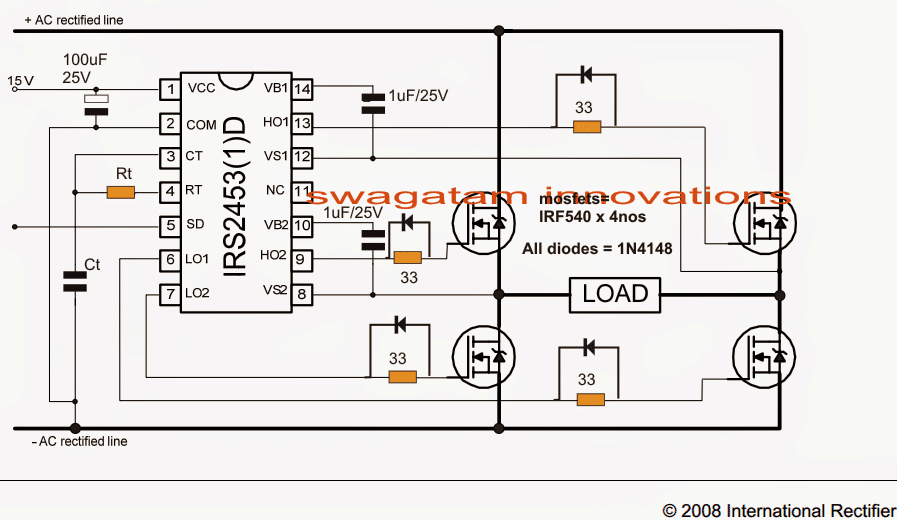

Parasti analogās PLL sastāv no analogās fāzes detektora, ar spriegumu kontrolējama oscilatora un zemfrekvences filtra. Līdzīgi digitālās fāzes bloķētā cilpa sastāv no digitālās fāzes detektora, a sērijas maiņas reģistrs , stabils vietējā pulksteņa signāls.

Digitālā fāzes bloķētā cilpa

Digitālās ieejas paraugus iegūst no saņemtā signāla, un šos paraugus uztver sērijas maiņas reģistrs, kuru virza pulksteņa impulsi, kas tiek piegādāti no lokālā pulksteņa signāla. Fāzes korektora ķēde, kas aizņem vietējo pulksteni, tiek izmantota, lai atjaunotu stabila pulksteņa signālu fāzē ar saņemto signālu, lēni pielāgojot fāzi, lai tas atbilstu saņemtajai signāla fāzei.

Šo korekciju var veikt, pamatojoties uz katra bita ātrgaitas paraugu, izmantojot korekcijas loģiku. Saņemtā signāla paraugs, kas iegūts, uztverot uztverto signālu vietējā pulksteņa ātrumā, tiek ievietots maiņu reģistrā.

Nepieciešamo fāzes korekciju var noteikt, novērojot saņemtā signāla paraugu kopumu. Tiek uzskatīts, ka abi pulksteņi ir fāzē tikai tad, ja saņemtā bita centrs atrodas maiņu reģistra centrā. Fāzes regulētājs ir paredzēts, lai kompensētu, ja reģenerētais pulkstenis atpaliek vai noved pie atsauces signāla.

Fāzes bloķētas cilpas pielietošana

- PLL bieži izmanto sinhronizācijas nolūkos un bitu sinhronizācijai, simbolu sinhronizācijai, saskaņotai demodulācijai un sliekšņa paplašināšanai kosmosa sakaros.

- Frekvenču modulētos signālus var demodulēt, izmantojot PLL.

- Jaunā frekvence, kas ir atsauces frekvences reizinājums radiosakaru raidītāji un sintezēts, saglabājot atskaites frekvences stabilitāti ar jaunu frekvenci, var sasniegt ar PLL.

- Daudzās saziņas sistēmās, datoros un daudzos ir daudz PLL lietojumprogrammu elektroniskās shēmas .

- Turpmāk aprakstītais PLL pielietojums apraksta PLL izmantošanu kā spriegumu līdz frekvences pārveidotājs .

Spriegums uz frekvences pārveidotāju (VFC), izmantojot PLL

Sakaru sistēmās ir nepieciešams nosūtīt signālus (šeit ņemiet vērā analogo signālu) ar lielu precizitāti. Šim nolūkam tiek izmantots sprieguma-frekvences pārveidotājs, jo ir viegli nosūtīt frekvences signālu, neradot traucējumus lielā attālumā, izmantojot optiskos izolatorus, koaksiālās vai vītā pāra līnijas, radio saites, optisko šķiedru saites .

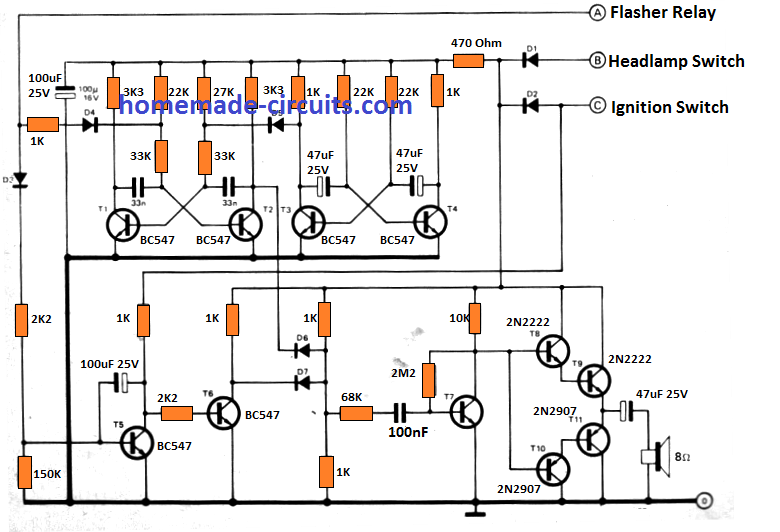

Ir divu veidu sprieguma-frekvences pārveidotāji, proti multivibratora tips VFC un uzlādes bilances tips VFC.

Multivibratora tips VFC

Multivibrators VFC

Multivibratora tipa VFC kondensators tiek uzlādēts un izlādēts, izmantojot strāvu, kas iegūta no ieejas sprieguma. Stabila atskaites ieeja tiek dota, lai iestatītu komutācijas sliekšņus, un izejas frekvence ir proporcionāla ieejas spriegumam un tām ir vienības atzīmes un telpas attiecība.

Uzlādes atlikuma tips VFC

Uzlādes atlikums VFC

Uzlādes bilance VFC sastāv no integratora, salīdzinātāja un precīzas uzlādes avota. Kad integratoram tiek ievadīta ieeja, tas tiek uzlādēts un, ja šī integratora izeja sasniedz salīdzināšanas slieksni, tiek aktivizēts uzlādes avots un fiksēta maksa tiek noņemts no integratora. Noņemtā lādiņa likmei jābūt vienādai ar piegādātā lādiņa ātrumu tā, lai uzlādes avota iedarbinātā frekvence un ievade integratoram būtu proporcionālas viena otrai.

Tādējādi šajā rakstā ir sniegts īss apraksts par fāzes bloķēta cilpas sistēma sakaru sistēmā. Šo rakstu var tehniski paplašināt, pamatojoties uz jūsu ieteikumiem un jautājumiem. Tādējādi jūs varat vērsties pie mums, lai saņemtu tehnisku palīdzību, zemāk ievietojot savus komentārus.