Komunikācijai ir būtiska loma iegultās sistēmas projektēšanā. Neizejot uz protokoliem, perifērijas paplašināšana ir ļoti sarežģīta un patērē lielu enerģiju. The iegultā sistēma būtībā izmanto sērijveida sakarus, lai sazinātos ar perifērijas ierīcēm.

Ir daudz sērijveida sakaru protokolu, piemēram, UART, CAN, USB, I2C un SPI sakari. Seriāls sakaru protokoli raksturlielumi ietver lielu ātrumu un mazu datu zudumu. Tas atvieglo projektēšanu sistēmas līmenī un nodrošina drošu datu pārsūtīšanu.

Seriālā datu komunikācija

Elektriski kodētu informāciju sauc par sērijas datiem, kurus pa protokoliem pa vienam bitam pārraida no vienas ierīces uz otru. Iegultā sistēmā vadības sensoru un izpildmehānismu dati tiek saņemti vai pārsūtīti uz kontroliera ierīcēm, piemēram, mikrokontrolleriem, lai dati tiktu tālāk analizēti un apstrādāti. Kad mikrokontrolleri strādā ar digitālajiem datiem, informācija no analogie sensori , izpildmehānismi un citas perifērijas ierīces tiek pārveidotas par vienu baitu (8 bitu) bināru vārdu, pirms tās tiek pārsūtītas uz mikrokontrolleru.

Seriālā datu komunikācija

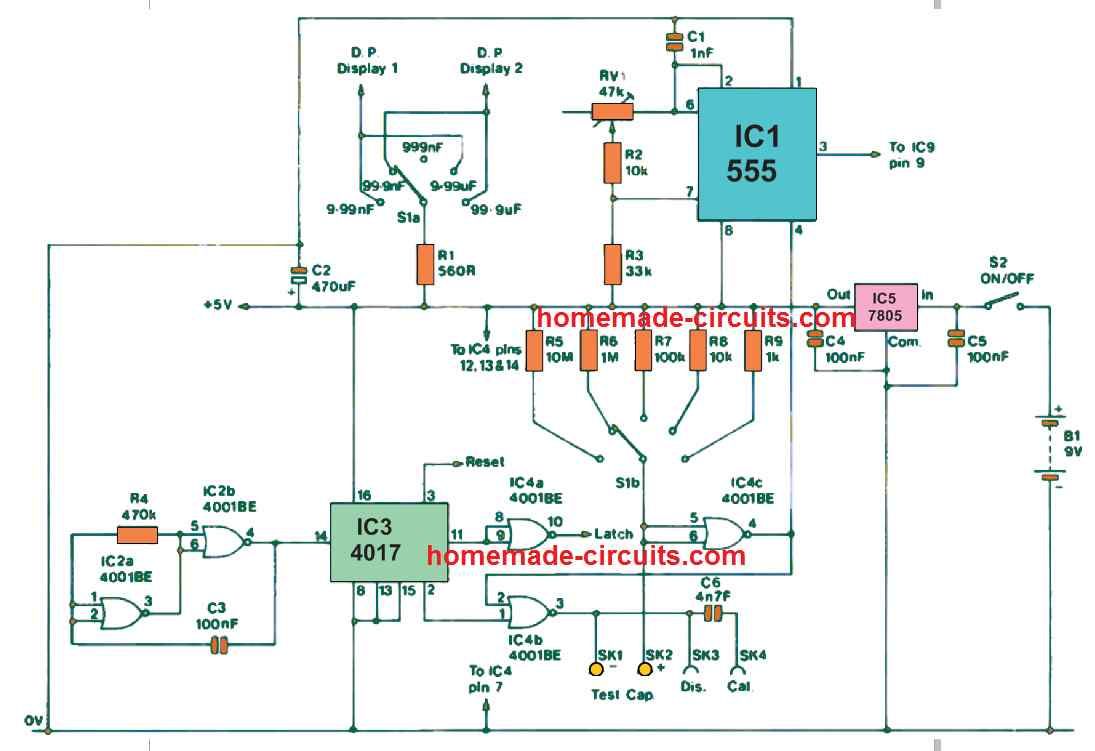

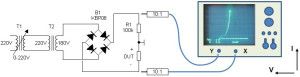

Šie sērijveida dati tiek pārraidīti attiecībā uz noteiktu pulksteņa impulsu. Datu pārraides ātrumu sauc par datu pārraides ātrumu. Datu bitu skaitu, kurus var pārraidīt sekundē, sauc par datu pārraides ātrumu. Pieņemsim, ka dati ir 12 baiti, pēc tam katrs baits tiek pārvērsts par 8 bitiem tā, lai kopējais datu pārraides lielums būtu aptuveni 96 biti / s datu (12 baiti * 8 biti vienā baitā). Ja datus var pārsūtīt reizi sekundē, datu pārraides ātrums ir aptuveni 96 biti / s vai 96 baudi. Displeja ekrāns reizi sekundē atsvaidzina datu vērtību.

Seriālās perifērās saskarnes pamati

SPI komunikācija nozīmē seriālo perifēro saskarni sakaru protokols , kuru Motorola izstrādāja 1972. gadā. SPI interfeiss ir pieejams populāros sakaru kontrolieros, piemēram, PIC, AVR un ARM kontrolieris utt. Tam ir sinhrona sērijveida sakaru datu saite, kas darbojas pilnā dupleksā, kas nozīmē, ka datu signāli vienlaikus virzās abos virzienos.

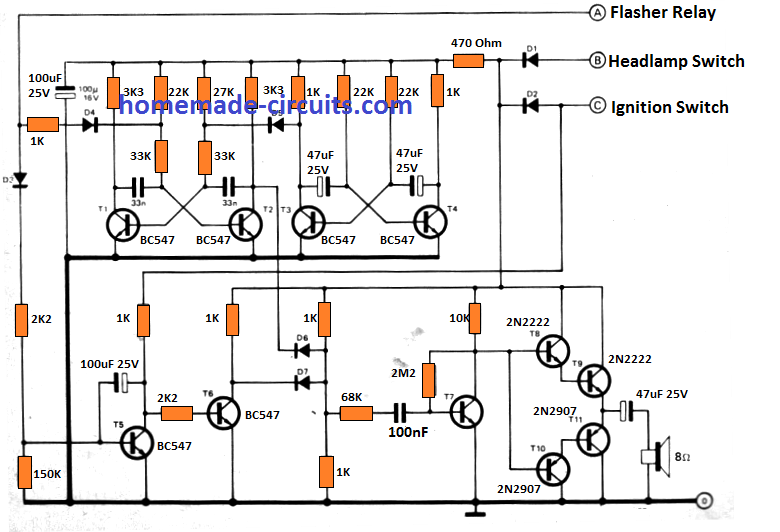

SPI protokols sastāv no četriem vadiem, piemēram, MISO, MOSI, CLK, SS, ko izmanto galvenā / verga saziņai. Kapteinis ir mikrokontrolleris, un vergi ir citas perifērijas ierīces, piemēram, sensori, GSM modems un GPS modems utt. Vairāki vergi tiek savienoti ar galveno, izmantojot SPI sērijas kopni. SPI protokols neatbalsta multi-master sakarus, un to izmanto īsā attālumā shēmas plates ietvaros.

Seriālās perifērās saskarnes pamati

SPI līnijas

MISO (Meistars vergā ārā) : MISO līnija ir konfigurēta kā ieeja galvenajā ierīcē un kā izeja vergu ierīcē.

MOSI (Master ārā vergu) : MOSI ir līnija, kas konfigurēta kā izeja galvenajā ierīcē un kā ieeja vergu ierīcē, kur to izmanto, lai sinhronizētu datu kustību.

SCK (sērijas pulkstenis) : Šo signālu vienmēr vada galvenais mehānisms sinhronai datu pārsūtīšanai starp galveno un vergu. To izmanto, lai sinhronizētu datu kustību gan iekšā, gan ārā caur MOSI un MISO līnijām.

SS (Slave Select) un CS (Chip Select) : Šis signāls tiek vadīts, lai izvēlētos atsevišķus vergus / perifērijas ierīces. Tā ir ievades līnija, ko izmanto, lai izvēlētos vergu ierīces.

Galvenā verga saziņa ar SPI sērijas autobusu

Single Master un Single Slave SPI ieviešana

Šeit saziņu vienmēr sāk kapteinis. Galvenā ierīce vispirms konfigurē pulksteņa frekvenci, kas ir mazāka vai vienāda ar maksimālo frekvenci, ko atbalsta vergu ierīce. Pēc tam kapteinis izvēlas saziņai vēlamo vergu, velkot konkrētās vergu ierīces mikroshēmas atlases līniju (SS), lai tā nonāktu zemā stāvoklī un būtu aktīva. Kapteinis ģenerē informāciju uz MOSI līniju, kas datus pārraida no galvenā uz vergu.

Meistara vergu komunikācija

Viena galvenā un vairāku vergu ieviešana

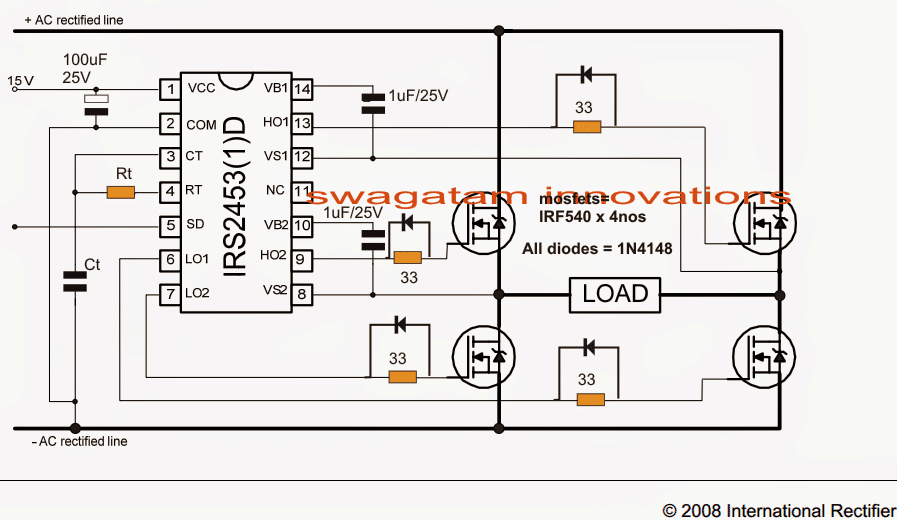

Šī ir vairāku vergu konfigurācija ar vienu galveno un vairākiem vergiem, izmantojot SPI sērijas kopni. Vairāki vergi ir savienoti paralēli galvenajai ierīcei ar SPI sērijas kopni. Šeit visas pulksteņa līnijas un datu līnijas ir savienotas kopā, bet mikroshēmas atlases tapa no katras vergu ierīces ir jāpievieno atsevišķai vergu atlases tapai masera ierīcē.

Viens kapteinis un vairāki vergi

Šajā procesā katras vergu ierīces vadību veic mikroshēmas atlases līnija (SS). Mikroshēmas atlases tapa ir zemāka, lai aktivizētu vergu ierīci, un augstu, lai atspējotu vergu ierīci.

Datu pārsūtīšana tiek organizēta, izmantojot nobīdes reģistrus gan galvenajās, gan vergu ierīcēs, kuru vārda lielums ir attiecīgi aptuveni 8 biti un 16 biti. Abas ierīces ir savienotas gredzena formā, lai masera maiņas reģistra vērtība tiktu pārsūtīta caur MOSI līniju, un pēc tam vergs pārvieto datus savā maiņu reģistrā. Datus parasti vispirms pārvieto ar MSB un pārvieto jauno LSB tajā pašā reģistrā.

Datu pārsūtīšana starp galveno un vergu

Pulksteņa polaritātes un fāzes nozīme

Parasti datu pārraide un saņemšana tiek veikta attiecībā pret pulksteņa impulsiem augšējās malās un krītošās malās. Uzlabotajiem mikrokontrolleriem ir divas frekvences: iekšējā frekvence un ārējā frekvence. SPI perifērijas ierīces varētu pievienot, koplietojot MISO, MOSI un SCLK līnijas. Perifērijas ierīces ir dažāda veida vai ātruma, piemēram, ADC, DAC utt. Tāpēc mums ir jāmaina SPCR iestatījumi starp pārsūtījumiem uz dažādām perifērijas ierīcēm.

SPCR reģistrs

SPI kopne darbojas vienā no 4 dažādiem pārsūtīšanas režīmiem ar pulksteņa polaritāti (CPOL) un pulksteņa fāzi (CPHA), kas nosaka izmantojamā pulksteņa formātu. Pulksteņa polaritāte un fāzes pulksteņa ātrums ir atkarīgs no tā, kuru perifērijas ierīci mēģināt sazināties ar galveno.

CPHA = 0, CPOL = 0: pirmais bits sākas kā zemāks signāls - datu paraugs tiek ņemts augšējā malā, un dati mainās, krītot malai.

CPHA = 0, CPOL = 1: Pirmais bits sākas ar zemāku pulksteni - dati tiek atlasīti krītošajā malā, un dati mainās, pieaugot malai.

CPHA = 1, CPOL = 0: Pirmais bits sākas ar augstāku pulksteni - dati tiek atlasīti krītošajā malā, un dati mainās, pieaugot malai.

CPHA = 1, CPOL = 1: Pirmais bits sākas ar augstāku pulksteni - datu paraugs tiek ņemts augšējā malā, un dati mainās, samazinoties malai.

SPI kopnes laiks

SPI sakaru protokols

Daudziem mikrokontrolleriem ir iebūvēti SPI protokoli, kas apstrādā visus sūtīšanas un saņemšanas datus. Jebkuru no datu režīma darbībām (R / W) kontrolē SPI protokola vadības un statusa reģistri. Šeit jūs varat novērot EEPROM saskarni PIC16f877a mikrokontrollerim, izmantojot SPI protokolu.

Šeit 25LC104 EEROM ir 131072 baitu atmiņa, kurā mikrokontrolleris pārsūta divus baitus datu uz EEROM atmiņa izmantojot SPI sērijas kopni. Šīs saskarnes programma ir sniegta zemāk.

Kapteiņa un verga komunikācija, izmantojot SPI sērijveida kopni

# iekļaut

Sbit SS = RC ^ 2

Sbit SCK = RC ^ 3

Sbit SDI = RC ^ 4

Sbit SDO = RC ^ 5

Atcelt inicializēt EEROM ()

Atcelt spēku ()

{

SSPSPAT = 0x00

SSPCON = 0x31

SMP = 0

SCK = 0

SDO = 0

SS = 1

EE_adress = 0x00

SPI_write (0x80)

SPI_write (1234)

SS = 0

}

SPI protokola priekšrocības

- Tā ir pilna dupleksa komunikācija.

- Tā ir ātrgaitas datu kopne 10MHz.

- Pārsūtīšanas laikā tas nav ierobežots ar 8 bitiem

- Aparatūras saskarne ir vienkārša, izmantojot SPI.

- Vergs izmanto galveno pulksteni, un tam nav nepieciešami vērtīgi oscilatori.

Tas viss ir par SPI sakariem un tā mijiedarbojas ar mikrokontrolleru . Mēs novērtējam jūsu lielo interesi un uzmanību par šo rakstu, un līdz ar to paredzam jūsu viedokli par šo rakstu. Turklāt par jebkuru saskarnes kodēšanu un palīdzību varat lūgt mums, komentējot tālāk.

Foto kredīti:

- Sērijas datu pārraide, ko veic Glotscotland

- Seriālās perifērās saskarnes pamati ni

- Viens kapteinis un vairāki vergi ēst

- Datu pārsūtīšana starp galveno un vergu inženieru garāža

- SPI autobusu laiks pēc maksimāli integrēts