The fāzes bloķēta cilpa ir viens no mūsdienu elektronisko sistēmu pamatblokiem. To parasti izmanto multivides, sakaru un daudzās citās lietojumprogrammās. Ir divi dažādi PLL veidi - lineāri un nelineāri. Nelineāro ir grūti un sarežģīti noformēt reālajā pasaulē, bet lineārās vadības teorija ir labi modelēta analogajās PLL. PLL ir pierādījis, ka lielākajai daļai elektronisko lietojumu ir pietiekams lineārs modelis.

Kas ir fāzes bloķēta cilpa?

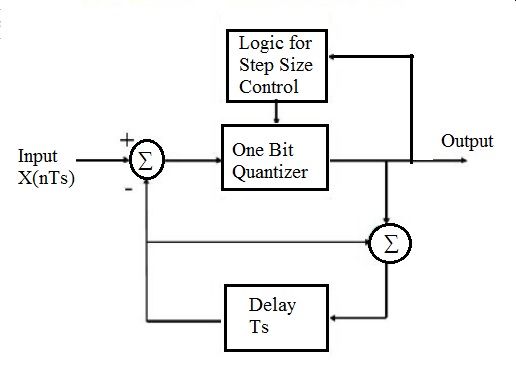

Fāzes bloķēta cilpa sastāv no fāzes detektora un ar spriegumu kontrolēta oscilatora. Fāzes detektora izeja ir sprieguma kontrolēta oscilatora (VCO) ieeja, un VCO izeja ir savienota ar vienu no fāzes detektora ieejām, kas parādīta zemāk pamata blokdiagrammā. Kad šīs divas ierīces tiek padotas viena otrai, izveidojas cilpa.

FĀZES AIZSLĒGTĀ CILVĒKA PAMATDIAGRAMMA

PLL blokshēma un darbības princips

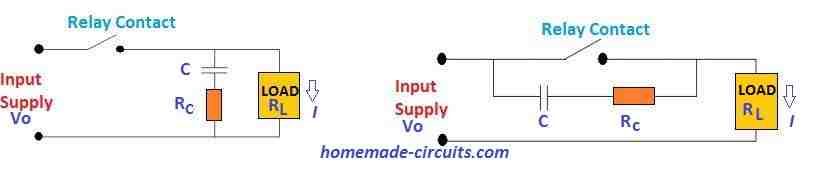

Fāzes bloķēta cilpa sastāv no fāzes detektora, a sprieguma kontrolēts oscilators un starp tiem ir fiksēts zemas caurlaidības filtrs. Ieejas signālu “Vi” ar ieejas frekvenci “Fi” atzīst fāzes detektors. Būtībā fāzes detektors ir salīdzinātājs kas salīdzina ieejas frekvenci fi caur atgriezeniskās saites frekvenci fo. Fāzes detektora izeja ir (fi + fo), kas ir līdzstrāvas spriegums. No fāzes detektora, t.i., līdzstrāvas spriegums tiek ievadīts zemfrekvences filtrā (LPF), tas noņem augstfrekvences troksni un rada vienmērīgu līdzstrāvas līmeni, t.i., Fi-Fo. Vf ir arī PLL dinamiska īpašība.

PLL blokshēma

Zemfrekvences filtra izeja, t.i., līdzstrāvas līmenis tiek nodots VCO. Ieejas signāls ir tieši proporcionāls VCO (fo) izejas frekvencei. Ieejas un izejas frekvences tiek salīdzinātas un pielāgotas, izmantojot atgriezenisko saiti, līdz izejas frekvence ir vienāda ar ieejas frekvenci. Tādējādi PLL darbojas kā brīva skriešana, uztveršana un fāžu bloķēšana.

Ja nav ievadīts ieejas spriegums, tad tiek uzskatīts, ka tas ir brīvi darbināms posms. Tiklīdz GOS pielietotā ieejas frekvence mainās un rada izejas frekvenci salīdzināšanai, to sauc par uztveršanas posmu. Zemāk redzamajā attēlā parādīta PLL blokshēma.

Fāzes bloķēts cilpas detektors

Fāzes bloķēta cilpas detektors salīdzina VCO ieejas frekvenci un izejas frekvenci, lai radītu līdzstrāvas spriegumu, kas ir tieši proporcionāls divu frekvenču fāžu atšķirībai. Analogie un ciparu signāli tiek izmantoti fāzes bloķētajā kontūrā. Lielākā daļa monolītā PLL integrētās shēmas izmantojiet analogo fāzes detektoru, un lielākā daļa fāzes detektoru ir no digitālā tipa. Divkāršā līdzsvara maisījuma ķēde parasti tiek izmantota analogās fāzes detektoros. Daži parastie fāzes detektori ir norādīti zemāk:

Ekskluzīvs VAI fāzes detektors

Ekskluzīvs VAI fāzes detektors ir CMOS IC 4070 tips. Ieejas un izejas frekvences tiek pielietotas fāzes detektoram EX OR. Lai iegūtu augstu izvadi, vismaz vienai ieejai jābūt zemai un pārējiem izvades apstākļiem ir zems, kas parādīts zemāk esošajā patiesības tabulā. Apsvērsim viļņu formu, ieejas un izejas frekvences, t.i., fi un fo fāžu starpība ir 0 grādi. Tad salīdzinātāja līdzstrāvas izejas spriegums būs fāzes starpības funkcija starp abām ieejām.

| būt | fo | Vdc |

zems | zems | zems |

zems | augsts | augsts |

augsts | Zems | augsts |

Augsts | Augsts | zems |

Fāžu starpības starp fi un fo funkcijas ir parādītas līdzstrāvas izejas sprieguma diagrammā. Ja fāzes detektors ir 180 grādi, tad izejas spriegums ir maksimālais. Ja gan ieejas, gan izejas frekvence ir kvadrātveida viļņi, tiek izmantoti šāda veida fāzes detektori.

Ekskluzīvs VAI fāzes detektors

Edge Trigger fāzes detektors

Malu sprūda fāzes detektors tiek izmantots, ja ieejas un izejas frekvences ir impulsa viļņu formā, kas ir mazāka par 50% darba ciklu. R-S flip flop tiek izmantots fāzes detektoriem, kas parādīts zemāk redzamajā attēlā. Uz no R-S flip flop , abi NOR vārti ir savstarpēji savienoti. Fāzes detektora izeja var mainīt tā loģisko stāvokli, iedarbinot R-S flip flop. Ieejas un izejas frekvenču pozitīvā mala var mainīt fāzes detektora izeju.

Edge Trigger fāzes detektors

Monolīts fāžu detektors

Monolīts fāzes detektors ir CMOS tips, t.i., IC 4044. To ļoti kompensē harmoniskā jutība, un darba cikla problēmas tiek atmestas, jo ķēde var reaģēt tikai uz ieejas signāla pāreju. Kritiskās lietojumprogrammās tas ir visdrudinātākais fāzes detektors. Neatkarīgajās amplitūdas variācijās nav fāzes kļūdas, izejas kļūdas sprieguma un ieejas viļņu formas darba cikla.

Fāzes bloķētas cilpas lietojumi

- FM demodulācijas tīkli FM darbībām

- To lieto motora ātruma vadība un izsekošanas filtri.

- To izmanto frekvences nobīdes dekodēšanā nesējfrekvences demodulācijai.

- To savlaicīgi izmanto digitālajiem pārveidotājiem.

- To lieto nervozēšanas mazināšanai, šķībuma nomākšanai, pulksteņa atjaunošanai.

Tas viss ir par fāzes bloķētās cilpas darbības un darbības principu un tā lietojumiem. Mēs ceram, ka rakstā sniegtā informācija jums palīdzēs uzzināt kaut ko par projektu un saprast to. Turklāt, ja jums ir kādi jautājumi par šo un turpmāko rakstu elektriskie un elektroniskie projekti jūs varat komentēt zemāk esošajā sadaļā. Šeit ir jautājums jums, kā vislabāk simulēt PLL stabilitātei?

Foto kredīti:

- PLL blokshēma shēma šodien

- Ekskluzīvs VAI fāzes detektors sanfoundry

- Edge Trigger fāzes detektors MĀCĪTIES-ELEKTRONIKA