ECL (emitter saistītās loģikas) pirmo reizi izgudroja IBM 1956. gada augustā Hannon S. Yourke. Šo loģiku sauc arī par pašreizējā režīma loģiku, ko izmanto IBM 7090 un 7094 datoros. ECL saime ir ļoti ātra, salīdzinot ar digitālā loģika ģimenes. Parasti šī loģiskā saime nodrošina izplatīšanās aizkavi, kas ir mazāka par 1 ns. Tā ir loģiskā saime, kuras pamatā ir bipolārā savienojuma tranzistori. Tā ir ātrākā loģikas saimes shēma, kas ir pieejama parastās loģikas sistēmas projektēšanai. Šajā rakstā ir apskatīts pārskats par emitētāja savienota loģika-shēma , strādājot ar lietojumprogrammām.

Kas ir emitētāja savienojuma loģika?

Ar emitētāju saistītā loģika ir vislabākā BJT Pamatota loģikas saime, ko izmanto parasto loģikas sistēmu projektēšanā. Dažreiz to sauc arī par pašreizējā režīma loģiku, kas ir ļoti ātrgaitas digitālā tehnoloģija. Parasti ECL tiek uzskatīts par ātrāko loģisko IC, kur tas sasniedz savu ātrgaitas darbību, izmantojot ļoti mazu sprieguma svārstību, kā arī izvairoties no tranzistoru iekļūšanas piesātinājuma reģionā.

ECL ieviešana izmanto pozitīvu barošanas spriegumu, kas pazīstams kā PECL vai pozitīvas atsauces ECL. Agrīnās ECL vārtos trokšņu imunitātes dēļ tiek izmantots negatīvs sprieguma padeve. Pēc tam pozitīvas atsauces ECL kļuva ļoti slavena, pateicoties tā saderīgākajiem loģikas līmeņiem, salīdzinot ar TTL loģikas saimēm.

Ar emitētāju savienotā loģika izkliedē milzīgu daudzumu statiskās jaudas, tomēr tās kopējais strāvas patēriņš ir zems, salīdzinot ar CMOS augstās frekvencēs. Tātad ECL galvenokārt ir izdevīgs pulksteņu sadales shēmās un lietojumprogrammās, kuru pamatā ir augstfrekvences.

Emitera savienotās loģikas funkcijas

ECL funkcijas ļaus tos izmantot daudzās augstas veiktspējas lietojumprogrammās.

- ECL nodrošina divas izejas, kas viena otru papildina vienmēr, jo ķēdes darbības pamatā ir diferenciālais pastiprinātājs.

- Šī loģiskā saime galvenokārt ir piemērota monolītām ražošanas metodēm, jo loģiskie līmeņi ir rezistoru attiecību funkcija.

- ECL saimes ierīces ģenerē piedāvātās funkcijas pareizo un papildu izvadi, neizmantojot ārējus invertorus. Līdz ar to tas samazina pakešu skaitu un jaudas prasības, kā arī samazina problēmas, kas rodas laika aizkaves dēļ.

- ECL ierīces diferenciālā pastiprinātāja konstrukcijā piedāvā plašu veiktspējas elastību, tāpēc ECL shēmas ļauj izmantot gan kā digitālās, gan lineārās shēmas.

- ECL vārtu konstrukcijai ir parasti augsta un zema ieejas pretestība, kas ir ārkārtīgi labvēlīga, lai sasniegtu lielu ventilatoru, kā arī piedziņas spēju.

- ECL ierīces ģenerē pastāvīgu strāvas aizplūšanu no barošanas avota, lai vienkāršotu barošanas avota konstrukciju.

- ECL ierīces, kas ietver atvērtā emitera izejas, vienkārši ļauj tām iekļaut pārvades līnijas piedziņas jaudu.

Emitera savienotā loģiskā shēma

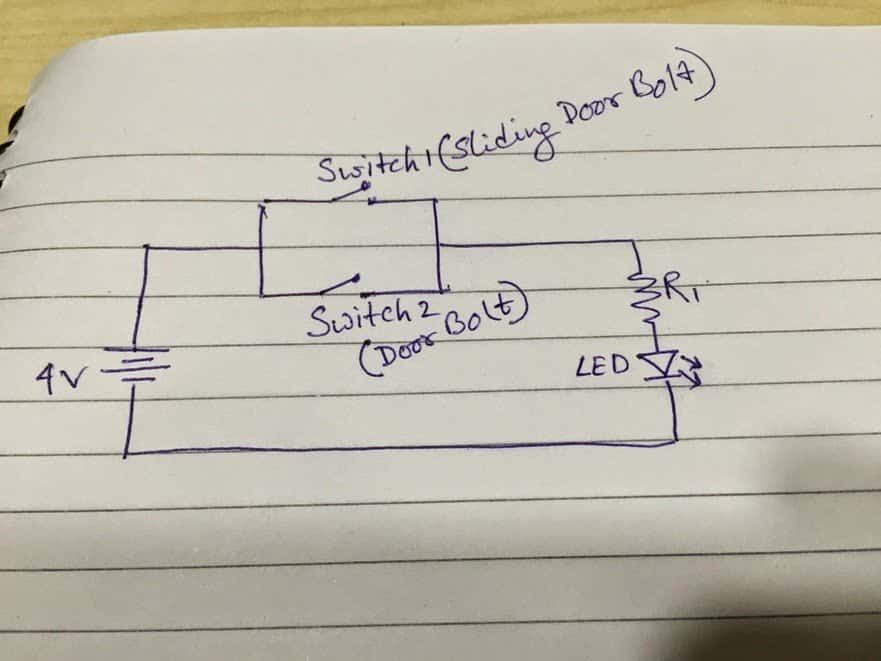

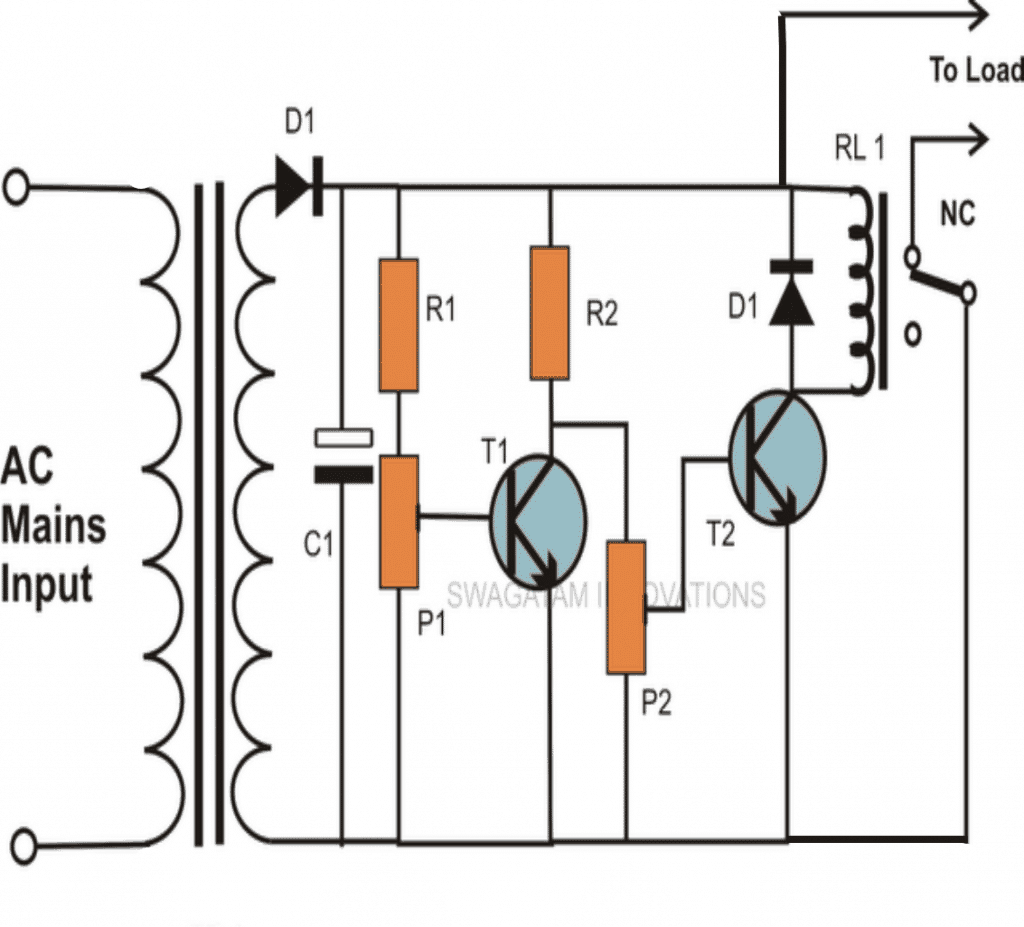

Zemāk ir parādīta ar emitētāju savienotā invertora loģiskā ķēde, kas ir izstrādāta ar rezistoriem un tranzistoriem. Šajā shēmā divu tranzistoru emitētāja spailes ir vienkārši savienotas ar strāvu ierobežojošo pretestību RE, ko izmanto, lai izvairītos no tranzistora piesātinājuma. Šeit tranzistora izeja tiek ņemta no kolektora spailes, nevis no emitera spailes. Šī shēma nodrošina divas izejas Vout (invertējošā izeja) un Vout2 (neinvertējošā izeja) un ieejas termināli, piemēram, Vin, kur tiek dota augsta vai zema ieeja. +Vcc = 5V.

Kā darbojas emitētāja savienotā loģika?

Ar emitētāju savienotās loģikas darbība ir tāda, ka ikreiz, kad ECL ķēdei tiek dota HIGH ieeja, tā ieslēgs 'Q1' tranzistoru un IZSLĒGTU Q2, bet Q1 tranzistors nav piesātināts. Tādējādi VOUT2 izvade tiks iestatīta uz HIGH un VOUT1 izvades vērtība būs LOW, jo samazināsies R1.

Līdzīgi, ja ECL piešķirtā VIN vērtība ir LOW, Q1 tranzistors tiks IZSLĒGTS un Q2 tranzistors IESLĒGTS. Tātad Q2 tranzistors nepārvietosies uz piesātinājumu. Tādējādi VOUT1 izvadei tiks izvilkta AUGSTA vērtība un VOUT2 izejas vērtība būs zema, jo samazināsies R2 pretestība.

Apskatīsim, kā tranzistors Q1 un Q2 ieslēdzas un izslēdzas, kad tiek pielikts spriegums.

Divi tranzistori, piemēram, Q1 un Q2, šajā ķēdē ir savienoti kā diferenciālais pastiprinātājs ar kopēju emitera rezistoru.

Šīs shēmas piemēra sprieguma padeve ir VCC = 5,0, VBB = 4,0 un VEE = 0 V. Ieejas AUGSTS un ZEMS līmeņa vērtības ir vienkārši definētas kā 4,4 V un 3,6 V. Faktiski šī ķēde ģenerē LOW izvades un AUGSTU līmeni, kas ir par 0,6 voltiem augstāks; tomēr tas tiek labots reālās ECL shēmās.

Kad Vin ir HIGH, Q1 tranzistors tiek ieslēgts, taču nav piesātināts, un Q2 tranzistors tiek izslēgts. Tātad, izejas spriegums, piemēram, VOUT2, caur R2 rezistoru tiek novilkts līdz 5 V, un var parādīt, ka sprieguma kritums pāri R1 rezistoram ir aptuveni 0,8 V, lai VOUT1 = 4,2 V (LOW). Turklāt VE = VOUT1 - VQ1 => 4,2 V - 0,4 V = 3,8 V, jo tranzistors Q1 ir pilnībā IESLĒGTS.

Kad Vin ir LOW, Q2 tranzistors tiks ieslēgts, bet nav piesātināts, un Q1 tranzistors tiek izslēgts. Tāpēc VOUT1 tiek pievilkts līdz 5,0 V, izmantojot R1 rezistoru, un var parādīt, ka VOUT2 ir 4,2 V. Arī VE => VOUT2 - VQ2 => 4,2 V - 0,8 V => 3,4 V, jo tranzistors Q2 ir ieslēgts.

ECL gadījumā abi tranzistori nekad nav piesātināti kā t ieejas / izejas sprieguma svārstības ir diezgan mazas, piemēram, 0,8 V un ieejas pretestība ir augsta, un izejas pretestība ir zema. Tas palīdz ECL darboties ātrāk ar mazāku izplatīšanās aizkaves laiku.

Divu ieejas izstarotāju savienota loģikas VAI/NOR vārtu ķēde

Tālāk ir parādīta divu ieejas emitētāju savienotā loģiskā VAI/NOR aizvara ķēde. Šī ķēde ir izstrādāta, pārveidojot iepriekš minēto invertora ķēdi. Modifikācija tiek veikta, pievienojot papildu tranzistoru ieejas pusē.

Šīs ķēdes darbība ir ļoti vienkārša. Ja ieejas, kas tiek izmantotas gan Q1, gan Q2 tranzistoriem, ir zemas, izvade1 (Vout1) tiks iestatīta uz AUGSTU vērtību. Tātad šis Vout1 atbilst NOR vārtu izvadei.

Tajā pašā laikā, ja Q3 tranzistors ir ieslēgts, tas padarīs otro izeju (Vout2) par HIGH. Tātad šī Vou2 izvade atbilst VAI vārtu izvadei.

Tādā pašā veidā, ja abas Q1 un Q2 tranzistoru ieejas ir HIGH, tas ieslēgs Q1 un Q2 tranzistorus un nodrošina zemu izvadi VOUT1 terminālī.

Ja Q3 tranzistors ir IZSLĒGTS šīs darbības laikā, tas nodrošinās augstu izvadi VOUT2 terminālī. Tātad, patiesības tabula VAI/NOR vārtiem ir sniegta zemāk.

|

Ievades |

Ievades | VAI |

NOR |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Izstarotāju savienojuma loģikas raksturlielumi

ECL īpašības ir šādas.

- Salīdzinot ar TTL, ECL ir ātrāks izplatīšanās laiks no 0,5 līdz 2 ns. Taču emitētāja savienojuma loģiskā jaudas izkliede ir lielāka, salīdzinot ar TTL, piemēram, 30 mW.

- ECL I/O spriegumiem ir nelielas svārstības, piemēram, 0,8.

- ECL ieejas pretestība ir augsta un izejas pretestība ir zema; līdz ar to tranzistors ļoti ātri maina savus stāvokļus.

- ECL ventilatora jauda ir augsta, un vārtu aizkaves ir mazas.

- ECL o/p loģika mainās no LOW uz HIGH, bet sprieguma līmeņi šiem stāvokļiem atšķirsies starp TTL un EC.

- ECL trokšņu noturība ir 0,4 V.

Priekšrocības un trūkumi

The ar emitētāju saistītās loģikas priekšrocības ir apspriesti turpmāk.

- ECL ventilators ir 25, kas ir labāks salīdzinājumā ar TTL, un tas ir zems salīdzinājumā ar CMOS.

- Vidējais ECL izplatīšanās aizkaves laiks ir no 1 līdz 4 ns, kas ir labāks salīdzinājumā ar CMOS un

- TTL. Tāpēc to sauc par ātrāko loģikas ģimeni.

- Kad BJT emitētājā ir savienoti loģikas vārti strādā aktīvajā reģionā, tad tiem ir maksimālais ātrums, salīdzinot ar visām loģikas saimēm.

- ECL vārti rada papildu izejas.

- Strāvas padeves vados nav strāvas pārslēgšanas tapas.

- Izejas var savienot kopā, lai nodrošinātu vadu VAI funkciju.

- ECL parametri temperatūras ietekmē daudz nemainās.

- No. no vienīgās mikroshēmas pieejamām funkcijām ir augsts.

The ar emitētāju saistītās loģikas trūkumi ir apspriesti turpmāk.

- Tam ir ārkārtīgi mazāka trokšņa robeža, t.i., ±200 mV.

- Jaudas izkliede ir augsta, salīdzinot ar citiem loģiskajiem vārtiem.

- Lai saskartos ar citām loģikas saimēm, ir nepieciešami līmeņa pārslēdzēji.

- Fanout ierobežo kapacitatīvo slodzi.

- Salīdzinot ar TTL , ECL vārti ir dārgi.

- Salīdzinot ar CMOS un TTL, ECL trokšņu imunitāte ir vissliktākā.

Lietojumprogrammas

Ar emitētāju saistītās loģikas pielietojumi ir šādi.

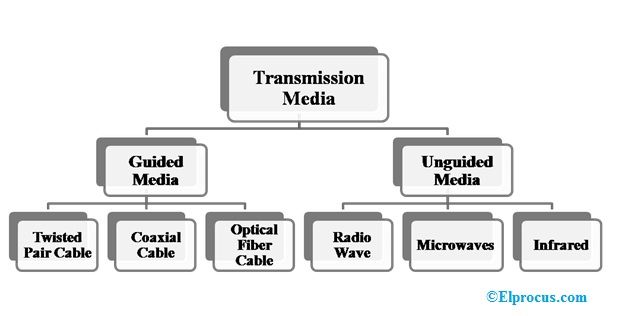

- Ar emitētāju savienotā loģika tiek izmantota kā loģikas un interfeisa tehnoloģija īpaši ātrdarbīgās sakaru ierīcēs, piemēram, optiskās šķiedras raiduztvērēju saskarnēs, Ethernet un ATM (asinhronā pārsūtīšanas režīma) tīklos.

- ECL ir loģikas saime, kuras pamatā ir BJT, un tās ātrgaitas darbību var panākt, izmantojot salīdzinoši nelielu sprieguma svārstību un izvairoties no tranzistoru pārvietošanās uz piesātinājuma reģionu.

- ECL tiek izmantots, veidojot ASLT shēmas IBM 360/91.

- ECL ļauj izvairīties no stacked tranzistoru izmantošanas, izmantojot viena gala nobīdes i/p un pozitīvu atgriezenisko saiti starp primārajiem un sekundārajiem tranzistoriem, lai sasniegtu invertora funkciju.

- ECL izmanto īpaši ātrdarbīgā elektronikā.

Tādējādi tas ir emitenta savienojuma loģikas pārskats vai ECL – ķēde, darbība, īpašības, raksturlielumi un lietojumi. ECL ir ļoti ātrākā loģikas saime, kuras pamatā ir BJT, salīdzinot ar citām digitālās loģikas ģimenēm. Tas sasniedz maksimālo ātrumu, izmantojot nelielu sprieguma svārstību un izvairoties no tranzistoru pārvietošanās piesātinājuma reģionā. Šī loģiskā saime nodrošina neticamu 1ns izplatīšanās aizkavi, un jaunākajās ECL saimēs šī aizkave ir samazināta. Šeit jums ir jautājums, kāds ir ECL alternatīvais nosaukums?