Ikdienā mēs sastopamies ar dažāda veida elektroniskajiem sīkrīkiem. Viena no tehnoloģijām, kas radīja revolūciju elektronikas ražošanā, ir “ Integrētā shēma “. Šī tehnoloģija samazināja elektronisko izstrādājumu izmēru, palielinot loģikas vārti par mikroshēmu. Šodien mums ir dažādi IC veidi un konfigurācijas. Kad mēs novērojam apkārt, mēs atklājam, ka dažus IC var izmantot tikai vienam konkrētam lietojumam, savukārt dažus IC var pārprogrammēt un izmantot dažādām lietojumprogrammām. Šie IC veidi tiek saukti par ASIC. Bet ar ko tās atšķiras? Kā ir iespējams tos pārprogrammēt? Kāpēc dažas IC nevar pārprogrammēt? Apskatiet, lai atrastu atbildes uz šiem jautājumiem.

Kas ir ASIC (lietojumprogrammas integrētā shēma)?

ASIC pilna forma ir Lietotnei specifiska integrētā shēma. Šīs shēmas ir specifiskas lietojumam, t.i. pielāgotas IC īpašam lietojumam. Tie parasti tiek izstrādāti no saknes līmeņa, pamatojoties uz konkrētā lietojuma prasībām. Daži no pamata lietojumprogrammu integrēto shēmu piemēri ir mikroshēmas, ko izmanto rotaļlietās, mikroshēmas, ko izmanto atmiņas un mikroprocesoru saskarnēm utt. ... Šīs mikroshēmas var izmantot tikai tai vienai lietošanai, kurai tās ir paredzētas. Jādomā, ka šie IC veidi dod priekšroku tikai tiem produktiem, kuriem ir liels ražošanas cikls. Tā kā ASIC ir izstrādāti no sakņu līmeņa, tiem ir augstas izmaksas un tie ir ieteicami tikai liela apjoma ražojumiem.

ASIC galvenā priekšrocība ir samazināts mikroshēmas izmērs, jo uz vienas mikroshēmas tiek uzbūvēts liels skaits ķēdes funkcionālo vienību. Mūsdienu ASIC parasti ietver 32 bitu mikroprocesors , atmiņas bloki, tīkla ķēdes utt ... Šāda veida ASIC ir pazīstami kā Sistēma mikroshēmā . Attīstoties ražošanas tehnoloģijai un pastiprināti pētot projektēšanas metodes, tiek izstrādāti ASIC ar dažādu līmeņu pielāgošanu.

ASIC veidi

ASIC tiek iedalīti kategorijās, pamatojoties uz pielāgošanas apjomu, ko programmētājs drīkst veikt mikroshēmā.

ASIC veidi

Pilns pasūtījums

Šāda veida projektā visas loģiskās šūnas ir pielāgotas konkrētam pielietojumam. dizainerim ir īpaši jāizveido loģiskās šūnas ķēdēm. Visi maskas slāņi savstarpējai savienošanai ir pielāgoti. Tātad programmētājs nevar mainīt mikroshēmas savstarpējos savienojumus, un, plānojot, viņam jāzina ķēdes izkārtojums.

Viens no labākajiem pilna pasūtījuma ASIC piemēriem ir mikroprocesors. Šāda veida pielāgošana ļauj dizaineriem vienā IC izveidot dažādas analogās shēmas, optimizētas atmiņas šūnas vai mehāniskās struktūras. Šī ASIC ražošana un projektēšana ir dārga un ļoti laikietilpīga. Šo IC izstrāde tiek patērēta apmēram astoņas nedēļas.

Parasti tie ir paredzēti augsta līmeņa lietojumiem. Maksimālā veiktspēja, minimizētā platība un visaugstākā elastības pakāpe ir galvenās Full Custom dizaina iezīmes. Galu galā risks ir augsts, jo loģiskās šūnas, rezistors utt. Izmantotie shēmas elementi netiek iepriekš pārbaudīti.

Daļēji pielāgots

Šāda veida projektā loģikas šūnas tiek ņemtas no standarta bibliotēkām, t.i. tie nav izgatavoti ar rokām, kā Pielāgotajā dizainā. Dažas maskas tiek pielāgotas, bet dažas tiek ņemtas no iepriekš izveidotas bibliotēkas. Pamatojoties uz bibliotēkā paņemto loģisko šūnu veidu un savstarpēji savienojumiem atļauto pielāgošanas apjomu, šīs ASIC tiek iedalītas divos tipos - standarta šūnā balstīta ASIC un Gate Array bāzes ASIC.

1). Standarta šūnas bāzes ASIC

Lai uzzinātu šīs IC, vispirms ļaujiet mums saprast, ko nozīmē standarta šūnu bibliotēka. Dažas loģiskās šūnas, piemēram, UN vārti, VAI vārti , multiplekseri, flip-flops dizaineri ir iepriekš izstrādājuši, izmantojot dažādas konfigurācijas, standartizēti un saglabāti bibliotēkas formā. Šī kolekcija ir pazīstama kā standarta šūnu bibliotēka.

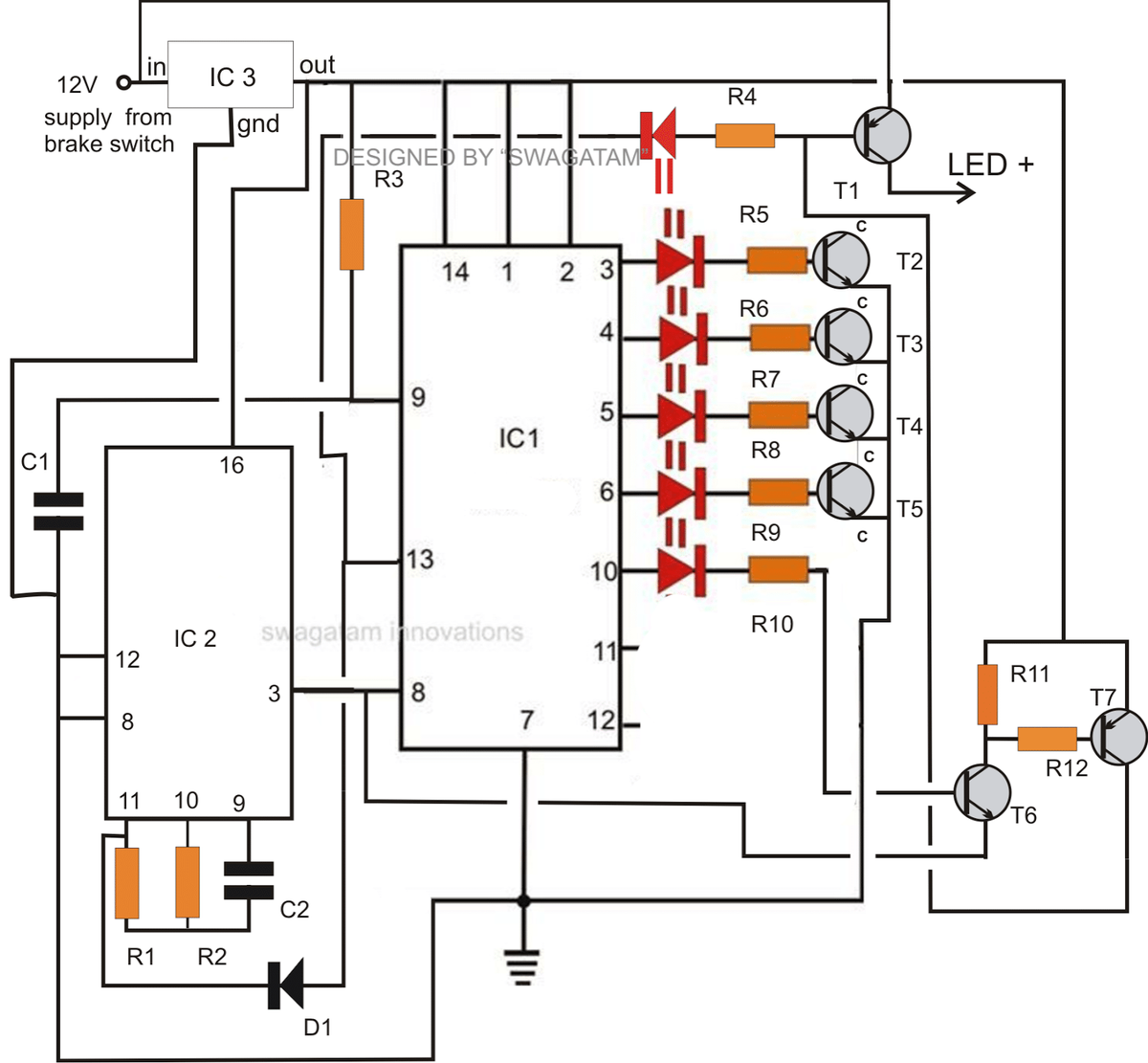

Standarta šūnu bāzes ASIC

Standarta šūnās tiek izmantotas ASIC loģiskās šūnas no šīm standarta bibliotēkām. ASIC mikroshēmā standarta šūnu laukumu vai elastīgo bloku veido standarta šūnas, kas sakārtotas rindu formā. Kopā ar šiem elastīgajiem blokiem mikroshēmās tiek izmantotas mega šūnas, piemēram, mikrokontrolleri vai pat mikroprocesori. Šīs mega šūnas ir pazīstamas arī kā megafunkcijas, sistēmas līmeņa makro, fiksētie bloki, funkcionālie standarta bloki.

Augšējais attēls attēlo standarta šūnu ASIC ar vienu standarta šūnu laukumu un četriem fiksētiem blokiem. Masku slāņi tiek pielāgoti. Šeit dizainers var ievietot standarta šūnas jebkur uz formas. Tie ir pazīstami arī kā C-BIC.

2). Vārtu masīva pamatā ASIC

Šāda veida daļēji pielāgoti ASIC ir iepriekš definēti tranzistori uz silīcija vafeles. t.i. projektētājs nevar mainīt tranzistoru izvietojumu uz formas. Bāzes masīvs ir iepriekš definēts vārtu masīva modelis, un bāzes šūna ir mazākā bāzes masīva atkārtotā šūna.

Projektētājam ir pienākums mainīt savstarpējo savienojumu starp tranzistoriem, izmantojot dažus pirmos matricas metāla slāņus. Dizainers izvēlas no vārtu masīvu bibliotēkas. Tos bieži sauc par Masku vārtu bloku. ASIC uz vārtu masīva bāzes ir trīs veidi. Tie ir Channeled Gate Array, Channel less gateway un strukturēti gate array.

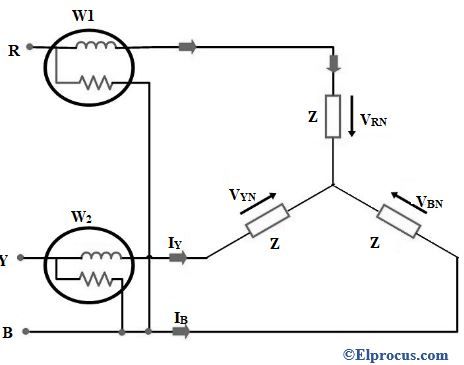

a). Kanālu vārtu masīvs

Šāda veida vārtu blokā starp tranzistoru rindām ir atstāta vieta elektroinstalācijai. Tie ir līdzīgi CBIC, jo tiek atstāta vieta savstarpējam savienojumam starp blokiem, bet novirzīto vārtu blokā šūnu rindas ir fiksētas augstumā, savukārt CBIC šo vietu var pielāgot.

Kanālu vārtu masīvs

Dažas no šī vārtu masīva galvenajām iezīmēm ir: šis vārtu masīvs savstarpēji savienošanai izmanto iepriekš definētas atstarpes starp rindām. Izgatavošanas laiks ir no divām dienām līdz divām nedēļām.

b). Kanāls bez vārtu masīva

Maršrutēšanai starp šūnu rindām nav atstāta brīva vieta, kā redzams novirzīto vārtu masīvā. Šeit maršrutēšana tiek veikta no augšas vārtu bloku šūnas, jo mēs varam pielāgot savienojumu starp metāla 1 un tranzistoriem. Maršrutēšanai mēs atstājam neizmantotus tranzistorus, kas atrodas maršrutēšanas ceļā. Ražošanas laiks ir apmēram divas nedēļas.

Kanāls bez vārtu masīva

c). Strukturēts vārtu masīvs

Šāda veida vārtu blokam ir iestrādāts bloks kopā ar vārtu bloku rindām, kā redzams iepriekš. Strukturētajam vārtu blokam ir augstāka CBIC laukuma efektivitāte. Tāpat kā maskēto vārtu blokam, tiem ir zemākas izmaksas un ātrāks apgriezienu skaits. Šeit fiksētais iegultās funkcijas izmērs ierobežo strukturēto vārtu bloku. Piemēram, vai šajā vārtu masīvā ir zona, kas rezervēta 32 k bitu kontrolierim, bet, ja lietojumprogrammā mums ir nepieciešama tikai 16 k bitu kontrollera zona, atlikusī platība tiek izšķiesta. Visu vārtu masīva darbības laiks ir no divām dienām līdz divām nedēļām un visiem ir pielāgots savstarpējs savienojums.

Strukturēts vārtu masīvs

Programmējams ASIC

Ir divu veidu programmējamie ASIC. Tie ir PLD un FPGA

PLD (programmējamās loģiskās ierīces)

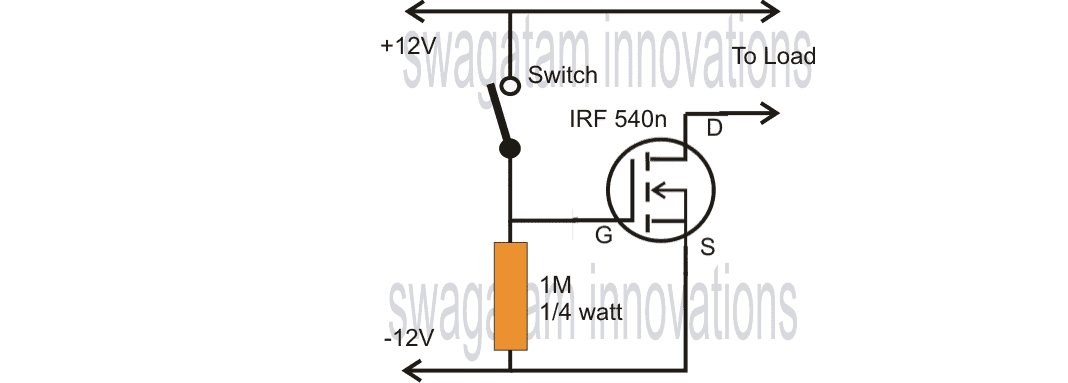

Šīs ir viegli pieejamās standarta šūnas. Mēs varam ieprogrammēt PLD, lai pielāgotu lietojumprogrammas daļu, tāpēc tie tiek uzskatīti par ASIC. Lai programmētu PLD, mēs varam izmantot dažādas metodes un programmatūru. Tie satur regulāru loģisko šūnu matricu, parasti programmējamu masīvu loģiku kopā ar flip-flops vai aizbīdņiem. Šeit savstarpējie savienojumi atrodas kā viens liels bloks.

PROM ir izplatīts šīs IC piemērs. EPROM kā savstarpēju savienojumu izmanto MOS tranzistorus, tāpēc, pielietojot augstspriegumu, mēs to varam ieprogrammēt. PLD nav pielāgotu loģisko šūnu vai tie nav savstarpēji savienoti. Tiem ir ātrs dizaina pagrieziens.

Programmējamās loģiskās ierīces

FPGA (laukā programmējams vārtu masīvs)

Ja PLD ir programmējama masīva loģika kā loģiskās šūnas FPGA ir vārtu blokam līdzīgs izkārtojums. PLD ir mazāki un mazāk sarežģīti nekā FPGA. Elastības un īpašību dēļ FPGA tiek aizstāta TTL mikroelektroniskās sistēmās. Dizaina pagrieziens ir tikai dažas stundas.

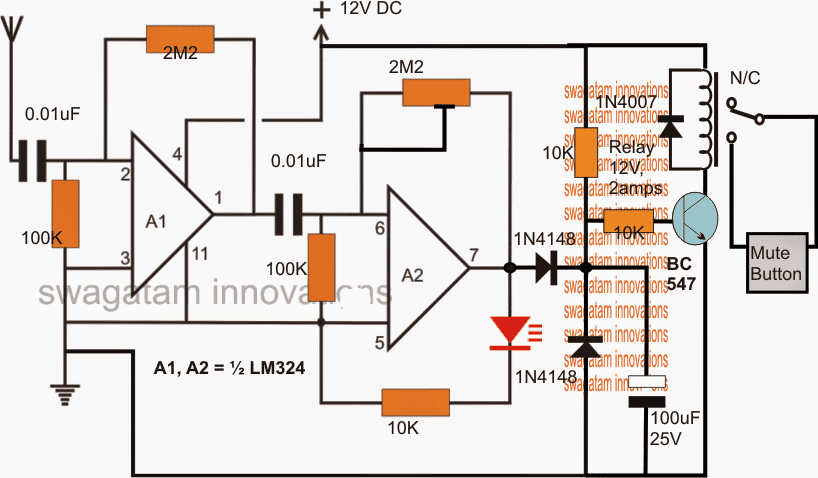

Laukā programmējams vārtu masīvs

Kodols sastāv no programmējamām loģiskām pamata šūnām, kas var veikt abus kombinācijas un secīga loģika . Mēs varam programmēt loģikas šūnas un savstarpēji savienoties, izmantojot dažas metodes. Pamata loģiskās šūnas ieskauj programmējamu savienojumu matrica, un kodolu ieskauj programmējamas I / O šūnas.

FPGA parasti sastāv no konfigurējamiem loģiskiem blokiem, konfigurējamiem I / O blokiem, programmējamiem savienojumiem, pulksteņa shēmām, ALU, atmiņas, dekoderiem.

Mēs esam redzējuši pieejamos dažādos ASIC veidus. Tagad sapratīsim, kad visi šie pielāgojumi un savstarpējie savienojumi tiek veikti ražošanas laikā.

Lietojumprogrammas integrētās shēmas (ASIC) projektēšanas plūsma

ASIC projektēšana tiek veikta pakāpeniski. Šī darbību secība ir pazīstama kā ASIC dizains Plūsma. Projektēšanas plūsmas soļi ir norādīti zemāk esošajā shēmā.

ASIC dizaina plūsma

Dizaina ieraksts: Šajā posmā dizaina mikroarhitektūra tiek realizēta, izmantojot aparatūras apraksta valodas, piemēram, VHDL, Verilog un System Verilog.

Loģikas sintēze: Šajā solī tiek izveidots izmantojamo loģisko šūnu, starpsavienojumu veidu un visu citu lietojumprogrammai nepieciešamo daļu tīkla saraksts, izmantojot HDL.

Sistēmas sadalīšana: Šajā solī mēs sadalām lielākoties izmēru matricas ASIC izmēra gabalos.

Pirms izkārtojuma simulācija: Šajā posmā tiek veikts simulācijas tests, lai pārbaudītu, vai projektā nav kļūdu.

Stāvu plānošana: Šajā posmā mikroshēmā tiek sakārtoti netlist bloki.

Izvietojums: Šajā posmā tiek izlemta šūnu atrašanās vieta blokā.

Maršrutēšana: Šajā solī tiek izveidoti savienojumi starp blokiem un šūnām. Ekstrakcija: Šajā solī mēs nosakām savstarpējās savienojuma elektriskās īpašības, piemēram, pretestības vērtību un kapacitātes vērtību.

Pēc izkārtojuma simulācija: Pirms modeļa iesniegšanas izgatavošanai šī simulācija tiek veikta, lai pārbaudītu, vai sistēma darbojas pareizi, kā arī starpsavienojuma slodzi.

ASIC piemēri

Zinot dažādas ASIC īpašības, tagad apskatīsim dažus ASIC piemērus.

Standarta šūnu ASIC: LCB 300k, 500k no LSI Logic Company, SIG1, 2, 3 ģimenes no ABB Hafo Inc., GCS90K no GCS Plessey.

Gate Array produkti: AUA20K no Harris Semiconductor, SCX6Bxx no National Semiconductors, TGC / TEC saimes no Texas Instruments.

PLD produkti: PAL Advanced Micro Devices saime, GAL saime no Philips Semiconductors, XC7300 un EPLD no XILINX.

FPGA produkti: XC2000, XC3000, XC4000, XC5000 sērija no XILINX, pASIC1 no QuickLogic, MAX5000 no Altera.

ASIC lietojumprogrammas

ASIC unikalitāte ir mainījusi elektronikas ražošanas veidu. Tie samazināja veidņu izmērus, vienlaikus palielinot loģikas vārti par mikroshēmu. ASIC parasti dod priekšroku augsta līmeņa lietojumprogrammām. ASIC mikroshēma tiek izmantota kā IP kodoli satelītiem, ROM ražošanai, Mikrokontrolleris un dažāda veida pielietojumi medicīnas un pētniecības nozarēs. Viena no populārākajām ASIC lietojumprogrammām ir BITCOIN MINER.

Bitcoin Miner

Kriptogrāfijas valūtas ieguvei nepieciešama lielāka jauda un ātrgaitas aparatūra. Vispārēja mērķa procesors ar lielu ātrumu nespēj nodrošināt tik lielu skaitļošanas jaudu. ASIC bitcoin kalnrači ir mikroshēmas, kas iebūvētas speciāli izstrādātās mātesplatēs un barošanas avoti , kas izveidota vienā vienībā. Tā ir mērķtiecīgi veidota aparatūra līdz pat mikroshēmu līmenim bitkoīnu ieguvei. Šīs vienības var izpildīt tikai vienas kriptogrāfijas valūtas algoritmu. Iespējams, ka cita veida kriptovalūtai mums ir nepieciešams cits kalnračs.

ASIC priekšrocības un trūkumi

The ASIC priekšrocības iekļaujiet sekojošo.

- Mazais ASIC izmērs padara to par labu izvēli sarežģītām lielākām sistēmām.

- Tā kā liels skaits ķēžu ir izveidotas vienā mikroshēmā, tas izraisa ātrgaitas lietojumprogrammas.

- ASIC ir zems enerģijas patēriņš.

- Tā kā tās ir mikroshēmas sistēma, ķēdes atrodas blakus. Tātad, lai savienotu dažādas shēmas, ir nepieciešams ļoti minimāls maršruts.

- ASIC nav laika problēmu un pēc ražošanas konfigurācijas.

The ASIC trūkumi iekļaujiet sekojošo.

- Tā kā tās ir pielāgotas mikroshēmas, tās nodrošina nelielu elastību programmēšanai.

- Tā kā šīs mikroshēmas ir jāprojektē no sakņu līmeņa, tām ir augstas izmaksas par vienību.

- ASIC ir lielāks laiks līdz tirgus starpībai.

ASIC vs FPGA

Atšķirība starp ASIC un FPGA ietver sekojošo.

ASIC | FPGA |

| Nav pārprogrammējams | Pārprogrammējams |

| Vēlams lielapjoma produkcijai | Vēlams maza apjoma ražojumiem |

| Tie ir specifiski lietojumprogrammām | Izmanto kā sistēmas prototipus |

| Energoefektivitāte prasa mazāk enerģijas | Mazāk energoefektivitāte prasa lielāku jaudu |

| Tās ir pastāvīgas shēmas, kuras laiku pa laikam nevar uzlabot. | Ļoti piemērots lietojumprogrammām, kurās shēma laiku pa laikam ir jāuzlabo, piemēram, mobilo telefonu mikroshēmas, bāzes stacijas utt |

Tādējādi tas viss ir par pārskatu par Lietotnei specifiska integrētā shēma . ASIC izgudrojums ir izraisījis milzīgas izmaiņas elektronikas izmantošanas veidā. Mēs izmantojam ASIC savā ikdienas dzīvē dažādu lietojumu veidā. Ar kādām ASIC lietojumprogrammām esat saskāries? Ar kāda veida ASIC jūs esat strādājis?