Secīga shēma ir loģiska ķēde, kur izeja ir atkarīga no ieejas signāla pašreizējās vērtības, kā arī no iepriekšējo ieeju secības. Kamēr a kombinācijas ķēde ir tikai pašreizējās ievades funkcija. Secīga shēma ir kombinētas shēmas un uzglabāšanas elementa kombinācija. secīgajās ķēdēs tiek izmantoti pašreizējie ieejas mainīgie un iepriekšējie ieejas mainīgie, kas tiek saglabāti un nodrošina datus ķēdei nākamajā pulksteņa ciklā.

Secīgu shēmu bloķēšanas diagramma

Secīgo shēmu veidi

The secīgas ķēdes tiek klasificēti divos veidos

- Sinhronā shēma

- Asinhronā shēma

Sinhronās secīgās ķēdēs ierīces stāvoklis mainās atsevišķos laikos, reaģējot uz pulksteņa signālu. Asinhronajās ķēdēs ierīces stāvoklis mainās, reaģējot uz mainīgajām ieejām.

Sinhronās shēmas

Sinhronajās ķēdēs ievadi ir impulsi ar noteiktiem impulsa platuma un izplatīšanās kavēšanās ierobežojumiem. Tādējādi sinhronās ķēdes var sadalīt pulksteņa un bez pulksteņa vai impulsa secīgās ķēdēs.

Sinhronā shēma

Pulkstenis secīgā shēma

Pulksteņa secīgajām ķēdēm ir atmiņas elementu flip-flops vai aizbīdņi. Visu ķēdes atmiņas elementu pulksteņa ieejām ir pievienots periodisks pulkstenis, lai sinhronizētu visas iekšējās stāvokļa izmaiņas. Tādējādi ķēdes darbību kontrolē un sinhronizē pulksteņa periodiskais impulss.

Cocked secīgs

Nepārtrauktā secīgā ķēde

Neapstiprinātā secīgā ķēdē ir nepieciešamas divas secīgas pārejas starp 0 un 1, lai mainītu ķēdes stāvokli. Neapstiprināta režīma ķēde ir paredzēta, lai reaģētu uz noteikta ilguma impulsiem, kas neietekmē ķēdes darbību.

Atbloķēta secība

Sinhronās loģikas ķēde ir ļoti vienkārša. Loģikas vārti kas veic darbības ar datiem, ir vajadzīgs noteikts laiks, lai reaģētu uz izmaiņām ievadā.

Asinhronās shēmas

Asinhronajai shēmai nav pulksteņa signāla, lai sinhronizētu tās iekšējās stāvokļa izmaiņas. Tādējādi stāvokļa maiņa notiek tieši reaģējot uz izmaiņām, kas notiek primārajās ievades līnijās. Asinhronajai shēmai nav nepieciešama precīza laika kontrole no flip-flops .

Asinhronā shēma

Asinhrono loģiku ir grūtāk noformēt, un tai ir dažas problēmas salīdzinājumā ar sinhrono loģiku. Galvenā problēma ir tā, ka digitālā atmiņa ir jutīga pret secību, kādā viņu ieejas signāli tos saņem, piemēram, ja divi signāli vienlaikus nonāk pie flip-flop, kurā stāvoklī ķēde nonāk, var būt atkarīgs no tā, kurš signāls nonāk pie loģikas vārti vispirms.

Asinhronās shēmas tiek izmantotas kritiskās sinhrono sistēmu daļās, kur sistēmas ātrums ir prioritāte, piemēram, kā mikroprocesori un ciparu signālu apstrādes shēmas .

Flip Flop ķēde

Flip-flop ir secīga ķēde, kas atlasa ievadi un maina izvadi noteiktā laika posmā. Tam ir divi stabili stāvokļi, un to var izmantot valsts informācijas glabāšanai. Signāli tiek lietoti vienai vai vairākām vadības ieejām, lai mainītu ķēdes stāvokli, un tiem būs viena vai divas izejas.

Tas ir secīgas loģikas un digitālo elektronisko sistēmu pamatelementu pamatkrātuves elements. Tos var izmantot, lai reģistrētu mainīgā vērtību. Flip-flop tiek izmantots arī ķēdes funkcionalitātes kontrolei.

RS Flip Flop

R-S flip-flop ir vienkāršākais flip-flop. Tam ir divas izejas, viena izeja ir pretēja otrai un divas ieejas. Divas ieejas ir Iestatīt un Atiestatīt. Flip-flop pamatā izmanto NAND vārtus ar papildu iespējošanas tapu. Kontūra dod izeju tikai tad, kad iespējošanas tapa ir augsta.

Blokshēma

SR Flip Flop blokshēma

Ķēdes shēma

SR Flip Flop shēmas diagramma

SR Flip Flop patiesības tabula

SR Flip Flop patiesības tabula

JK Flip Flop

JK flip-flop ir viens no svarīgiem flip-flops. Ja J un K ieejas ir vienas un kad tiek piemērots pulkstenis, izeja mainās neatkarīgi no iepriekšējiem apstākļiem. Ja J un K ieejas ir 0 un, kad tiek piemērots pulkstenis, izejā nemainīsies. JK flip-flop nav nenoteikta stāvokļa.

Ķēdes shēma

JK Flip Flop ķēde

JK Flip Flop patiesības tabula

JK Flip Flop patiesības tabula

D Flip Flop

D flip-flop ir viena datu līnija un pulksteņa ievade D flip-flop ir SR flip-flop vienkāršošana . D flip-flop ieeja nonāk tieši ieejā S un kompliments - ieejā R. D ieeja tiek atlasīta visu pulksteņa impulsu.

Ķēdes shēma

D flip flop ķēde

D flip flop Patiesības tabula

D flip flop Patiesības tabula

T Flip Flop

Tā ir metode, kā izvairīties no nenoteikta stāvokļa, kas atrodams RS flip-flop procesā. Tas nodrošina tikai vienu ieeju, t.i., T ieeju. Šis flip-flop darbojas kā Toggle slēdzis. Pārslēgt nozīmē mainīt uz citu stāvokli. T flip-flop ir veidots no pulksteņa RS flip-flop.

Ķēdes shēma

T Flip Flop ķēde

T Flip Flop patiesības tabula

T Flip Flop patiesības tabula

Elektroniskais oscilators

Elektroniskais oscilators ir elektroniska shēma, kas rada periodiskus, svārstīgus signālus. Oscilators pārveido līdzstrāvu no barošanas avota maiņstrāvas signālā.

Elektroniskais oscilators

Oscilators ir pastiprinātājs, kas nodrošina atgriezenisko saiti ar ieejas signālu. Tā ir rotējoša ierīce, kas ražo maiņstrāvu. Lai oscilators pats darbotos, ieejas ķēdei jāpievieno pietiekami daudz enerģijas. Atgriezeniskās saites signāls oscilatorā ir reģeneratīvs.

Elektroniskos oscilatorus klasificē divās kategorijās

- Sinusoidālais vai harmoniskais oscilators

- Ne sinusoidāls vai relaksācijas oscilators

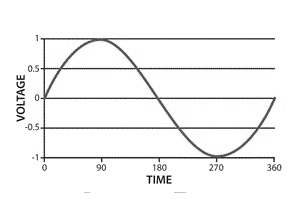

Sinusoidālais vai harmoniskais oscilators

Oscilatori, kas dod izeju kā sinusa viļņu, tiek saukti par sinusoidālajiem oscilatoriem. Šie oscilatori var nodrošināt izvadi frekvencēs no 20Hz līdz GHz. Sinusoidālos oscilatorus atkarībā no oscilatorā izmantotā materiāla vai komponentiem turpmāk iedala četros veidos

- Noregulēts ķēdes oscilators

- RC oscilators

- Kristāla oscilators

- Negatīvās pretestības oscilators

Ne sinusoidāls vai relaksācijas oscilators

Ne sinusoidālie oscilatori nodrošina izvadi kvadrātveida, taisnstūrveida vai zāģveida zobu viļņu formā. Šie oscilatori var nodrošināt izvadi frekvencēs no 0 līdz 20MHz.

Secīgu loģisko shēmu pielietojums

Secīgo loģisko shēmu galvenie pielietojumi ir:

- Kā lete , maiņu reģistrs, flip-flops.

- Izmanto, lai izveidotu atmiņas bloku.

- Kā programmējamas ierīces (PLD, FPGA, CPLD)

Tas viss ir par secīgām ķēdēm. Secīgās ķēdes ir ķēdes, kur izejas tiešā vērtība ir atkarīga no tiešajām ieeju vērtībām un arī no stāvokļiem, kādos tās bija iepriekš. Tie satur atmiņas blokus ķēdes iepriekšējā stāvokļa saglabāšanai.

Turklāt, ja jums ir kādi jautājumi par šo rakstu vai jebkāda palīdzība elektrisko un elektronisko projektu īstenošanā, varat vērsties pie mums, komentējot tālāk komentāru sadaļā. Šeit ir jautājums jums, Ko nozīmē secīgas shēmas?