Vadības bloks ir galvenā centrālā procesora (CPU) sastāvdaļa datoros, kas var vadīt darbības programmas izpildes laikā, izmantojot procesors / dators. Vadības ierīces galvenā funkcija ir iegūt un izpildīt instrukcijas no datora atmiņas. Tas saņem ievadīšanas instrukciju / informāciju no lietotāja un pārveido to vadības signāli , kas pēc tam tiek nodoti CPU tālākai izpildei. Tas ir iekļauts kā daļa no Fona Neimaņa arhitektūras, kuru izstrādājis Džons Neimans. Tas ir atbildīgs par laika signālu un vadības signālu nodrošināšanu, un CPU vada programmas izpildi. Mūsdienu datoros tas ir iekļauts kā CPU iekšēja daļa. Šajā rakstā ir aprakstīta pilnīga informācija par vadības bloku.

Kas ir vadības bloks?

Komponents, kas saņem ieejas signālu / informāciju / instrukciju no lietotāja un pārveido par vadības signāliem izpildei CPU. Tas kontrolē un vada galveno atmiņu, aritmētisko un loģisko vienību (ALU), ievades un izvades ierīces, kā arī atbild par instrukcijām, kas tiek nosūtītas uz datora centrālo procesoru. Tas paņem instrukcijas no galvenā atmiņa procesora un nosūta procesora instrukciju reģistram, kurā ir reģistra saturs.

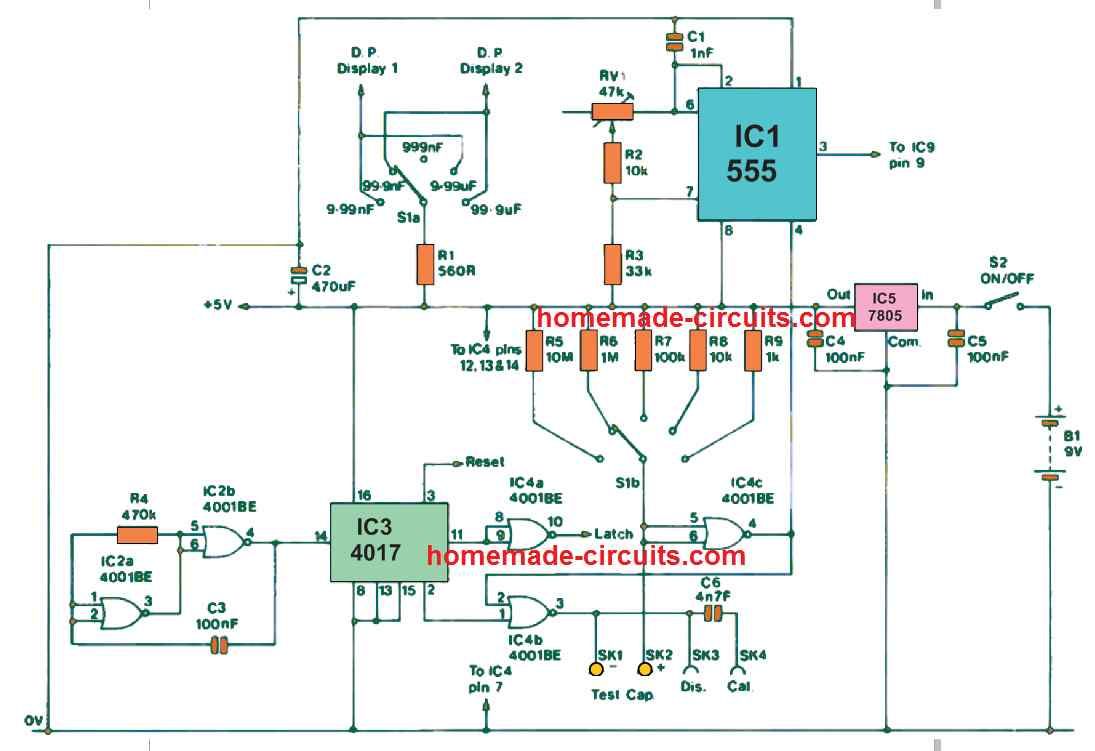

Vadības bloka blokshēma

Vadības bloks pārveido ieeju vadības signālos un pēc tam nosūta procesoram un vada programmas izpildi. Veicamās operācijas datorā vada procesors. Galvenokārt centrālais procesors (CPU) un Grafiskā apstrādes vienība (GPU) kā vadības daļu ir nepieciešama vadības ierīce. Vadības bloka blokshēma ir parādīta iepriekš.

Vadības bloka komponenti

Šīs vienības sastāvdaļas ir instrukcijas reģistrus , vadības signāli CPU, vadības signāli uz / no kopnes, vadības kopne, ievades karodziņi un pulksteņa signāli.

Vadu vadības bloka komponenti ir instrukciju reģistrs (satur opkodu un adreses lauku), laika vienība, vadības stāvoklis ģenerators , vadības signāla ģenerēšanas matrica un instrukciju dekodētājs.

Micro programmētās vadības bloka sastāvdaļas ir nākamais adrešu ģenerators, vadības adrešu reģistrs, vadības atmiņa un vadības datu reģistrs.

Funkcijas

The vadības bloka funkcijas iekļaujiet sekojošo.

- Tas vada datu secības plūsmu starp procesoru un citām ierīcēm.

- Tas var interpretēt instrukcijas un kontrolēt datu plūsmu procesorā.

- Tas ģenerē vadības signālu secību no saņemtajām instrukcijām vai komandām no komandu reģistra.

- Tā ir atbildīga par tādu izpildes vienību kā ALU, datu buferu un reģistru kontroli datora CPU.

- Tam ir iespēja ienest, atšifrēt, apstrādāt izpildi un saglabāt rezultātus.

- Tas nevar apstrādāt un saglabāt datus

- Lai pārsūtītu datus, tas sazinās ar ievades un izvades ierīcēm un kontrolē visas datora vienības.

Vadības bloka dizains

To var noformēt, izmantojot divus vadības bloka veidi kas ietver sekojošo.

- Pamatojoties uz vadu

- Mikroprogrammēta (vienlīmeņa un divu līmeņu)

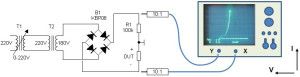

Vadu vadība

Vadu vadības bloka konstrukcija ir parādīta iepriekš. Šāda veida vadības signālus ģenerē īpaša aparatūra loģiskā shēma bez izmaiņām ķēdes struktūrā. Šajā gadījumā ģenerēto signālu nevar pārveidot izpildei procesorā.

Opkoda pamatdati (instrukcijas darbības kods tiek nosūtīts uz dekodētāju instrukciju dekodēšanai dekodētājs ir dekodētāju komplekts dažādu veidu datu atšifrēšanai opkodā. Tā rezultātā rodas izejas signāli, kas satur aktīvo signālu vērtības, kas tiek ievadītas kā ievads matricas ģeneratoram, lai ģenerētu vadības signālus programmas izpildei, ko veic datora procesors.

Vadības ierīce, kas balstīta uz vadu

Matricas ģenerators nodrošina vadības bloka stāvokļus un signālus, kas tiek izvadīti no procesora (pārtraukuma signāli). Matrica ir veidota kā programmējams loģiskais masīvs . Matricas ģeneratora radītie vadības signāli tiek doti kā nākamā ģeneratora matricas ieeja un apvienojas ar laika vienības laika signāliem, kas satur taisnstūrveida modeļus.

Lai iegūtu jaunu instrukciju, vadības bloks pārvēršas par sākuma posmu jaunu komandu izpildei. Vadības bloks paliek sākotnējā vai pirmajā posmā, kamēr datora laika signāli, ieejas signāli un instrukcijas nav mainīti. Vadības bloka stāvokļa izmaiņas var palielināt, ja mainās kāds no ģenerētajiem signāliem.

Kad notiek ārējs signāls vai pārtraukums, vadības bloks pāriet uz nākamo stāvokli un veic pārtraukuma signāla apstrādi. Karodziņus un stāvokļus izmanto, lai atlasītu vēlamos stāvokļus, lai izpildītu instrukcijas izpildes ciklu.

Pēdējā stāvoklī vadības bloks iegūst nākamo instrukciju un nosūta izvadi uz programmas skaitītāju, pēc tam uz atmiņas adrešu reģistru, uz bufera reģistru un pēc tam uz instrukciju reģistru, lai lasītu instrukciju. Visbeidzot, ja pēdējā instrukcija (kuru ienes vadības bloks) ir beigu instrukcija, tad tā pāriet uz procesora darbības stāvokli un gaida, kamēr lietotājs vada nākamo programmu.

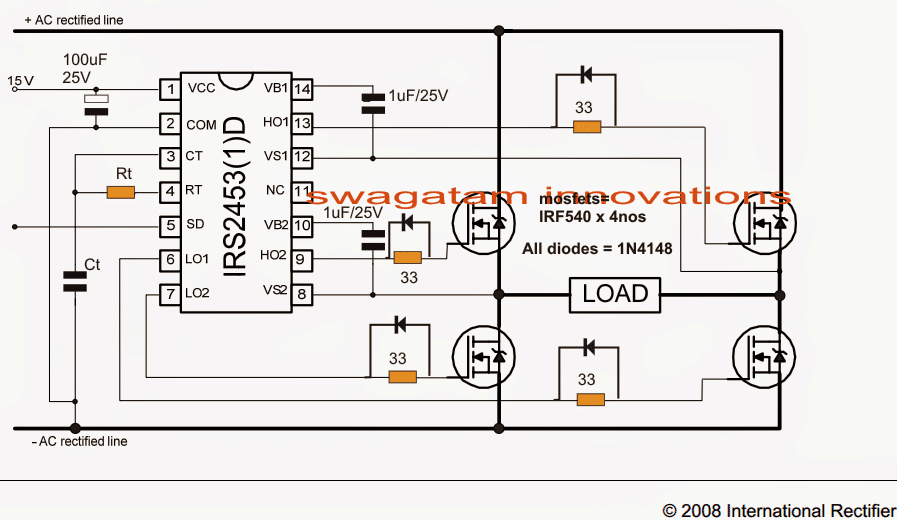

Mikroprogrammēta vadības ierīce

Šajā tipā vadības krātuve tiek izmantota vadības signālu glabāšanai, kas tiek kodēti programmas izpildes laikā. Vadības signāls netiek ģenerēts uzreiz un tiek dekodēts, jo mikroprogramma glabā adreses lauku vadības krātuvē. Viss process ir vienots līmenis.

Mikrooperācijas tiek veiktas mikrouzdevumu izpildei programmā. Micro programmētās vadības bloka diagramma ir parādīta iepriekš. No diagrammas mikrokomandu adrese tiek iegūta no vadības atmiņas adrešu reģistra. Visa vadības bloka informācija tiek pastāvīgi saglabāta vadības atmiņā ar nosaukumu ROM.

Mikroprogrammēta vadības ierīce

Mikroinstrukciju no vadības atmiņas tur vadības reģistrs. Tā kā mikro-instrukcija ir vadības vārda formā (satur bināras kontroles vērtības), datu apstrādei nepieciešama 1 vai vairākas mikrooperācijas.

Mikrokomandu izpildes laikā nākamais adrešu ģenerators aprēķināja nākamo mikrokomandu adresi un pēc tam nosūta uz vadības adrešu reģistru, lai lasītu nākamo mikrokomandu.

Mikroprogrammas mikrooperāciju secību veic nākamais adrešu ģenerators un darbojas kā mikroprogrammu sekvencētājs, lai iegūtu secības adresi, t.i., nolasītu no vadības atmiņas.

Verilog kods vadības blokam

Vadības ierīces Verilog kods ir parādīts zemāk.

`ietver“ prj_definition.v ”

modulis CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA, CL_DATA

// Izejas signāli

// Reģistra faila izejas

izeja [`DATA_INDEX_LIMIT: 0] RF_DATA_W

izvade [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

izvade RF_READ, RF_WRITE

// ALU izejas

izeja [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

izeja [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Atmiņas izejas

izeja [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

izvade MEM_READ, MEM_WRITE

// Ieejas signāli

ievade [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

ievade ZERO, CLK, RST

// Inout signāls

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Valsts tīkli

vads [2: 0] proc_state

// satur programmas skaitītāja vērtību, saglabā pašreizējo instrukciju, kaudzes rādītāju reģistru

reģ. MEM_READ, MEM_WRITE

reģ. MEM_ADDR

reģ ALU_OP1, ALU_OP2

reģ ALU_OPRN

reģ. RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reģ. RF_DATA_W

reģ. [1: 0] stāvoklis, nākamā stacija

PROC_SM stāvokļa mašīna (.STATE (proc_state), CLK (CLK), RST (RST))

vienmēr @ (posedge CLK)

sākt

ja (RST)

Valsts<= RST

cits

Valsts<= next_state

beigas

vienmēr @ (valsts)

sākt

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

lieta (valsts)

`PROC_FETCH: sākt

next_state = 'PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

beigas

`PROC_DECODE: sākt

next_state = 'PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

beigas

`PROC_EXE: sākt

next_state = 'PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

beigas

`PROC_MEM: sākt

next_state = 'PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

beigas

'PROC_WB: sākt

next_state = 'PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

beigas

endcase

beigas

endmodulis

modulis PROC_SM (VALSTS, CLK, RST)

// izejvielu saraksts

ieeja CLK, RST

// rezultātu saraksts

izvade [2: 0] VALSTS

// ievades saraksts

ieeja CLK, RST

// izvades saraksts

izeja STATE

reģ. [2: 0] VALSTS

reģ. [1: 0] stāvoklis

reg [1: 0] nākamā stacija

reģ. PC_REG, INST_REG, SP_REF

`definē PROC_FETCH 3’ h0

`definē PROC_DECODE 3’ h1

`definē PROC_EXE 3’h2

`definē PROC_MEM 3’h3

`definē PROC_WB 3’h4

// stāvokļa ierosināšana

sākotnējais

sākt

štats = 2’bxx

next_state = 'PROC_FETCH

beigas

// atiestatīt signāla apstrādi

vienmēr @ (posedge RST)

sākt

statuss = 'PROC_FETCH

next_state = 'PROC_FETCH

beigas

vienmēr @ (posedge CLK)

sākt

stāvoklis = nākamā stacija

beigas

vienmēr @ (valsts)

sākt

ja (norādiet === 'PROC_FETCH)

sākt

next_state = 'PROC_DECODE

print_instruction (INST_REG)

beigas

ja (norādiet === 'PROC_DECODE)

sākt

next_state = 'PROC_EXE

beigas

ja (norādiet === 'PROC_EXE)

sākt

next_state = 'PROC_MEM

print_instruction (SP_REF)

beigas

ja (norādiet === 'PROC_MEM)

sākt

next_state = 'PROC_WB

beigas

ja (norādiet === 'PROC_WB)

sākt

next_state = 'PROC_FETCH

print_instruction (PC_REG)

beigas

beigas

uzdevuma drukāšanas_norādījums

ievade [`DATA_INDEX_LIMIT: 0] inst

reģ [5: 0] opkods

reģ. [4: 0] rs

reģ. [4: 0] rt

reģ. [4: 0]

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] tūlītēja reg [25: 0] adrese

sākt

// parsēt instrukciju

// R-tips

{opcode, rs, rt, rd, shamt, funct} = inst

// es-tips

{opcode, rs, rt, tūlītējs} = inst

// J tips

{opcode, address} = inst

$ write (“@% 6dns -> [0X% 08h]”, $ time, inst)

reģistrs (opcode) // R-Type

6'h00: sākums

gadījums (funkcija)

6’h20: $ write (“pievienot r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h22: $ write (“sub r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h2c: $ write (“mul r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h24: $ write (“un r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h25: $ write (“vai r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h27: $ write (“ne r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h2a: $ write (“slt r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h00: $ write (“sll r [% 02d],% 2d, r [% 02d]”, rs, shamt, rd)

6’h02: $ write (“srl r [% 02d], 0X% 02h, r [% 02d]”, rs, shamt, rd)

6’h08: $ write (“jr r [% 02d]”, rs)

noklusējums: $ write (“”)

endcase

beigas

// es-tips

6’h08: $ write (“addi r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h1d: $ write (“muli r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h0c: $ write (“andi r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h0d: $ write (“ori r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h0f: $ write (“lui r [% 02d], 0X% 04h”, rt, tūlītējs)

6’h0a: $ write (“slti r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h04: $ write (“beq r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h05: $ write (“bne r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h23: $ write (“lw r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

6’h2b: $ write (“sw r [% 02d], r [% 02d], 0X% 04h”, rs, rt, tūlītējs)

// J-tips

6’h02: $ write (“jmp 0X% 07h”, adrese)

6’h03: $ write (“jal 0X% 07h”, adrese)

6’h1b: $ write (“push”)

6’h1c: $ write (“pop”)

noklusējums: $ write (“”)

endcase

$ write (“ n”)

beigas

endtask

beigu modulis

Bieži uzdotie jautājumi

1). Kāds ir vadības bloka darbs?

Vadības bloka darbs ir virzīt datu plūsmu vai instrukcijas datora procesora izpildei. Tas kontrolē, pārvalda un koordinē galveno atmiņu, ALU, reģistrus, ievades un izvades vienības. Tas paņem instrukcijas un ģenerē izpildes vadības signālus.

2). Kāda ir vadības atmiņa?

Vadības atmiņa parasti ir RAM vai ROM, lai saglabātu vadības reģistra adresi un datus.

3). Kas ir Wilkes vadības bloks?

Secīgā un kombinētās shēmas vadu vadības bloku nomaina Wilkes vadības bloks. Tas izmanto atmiņas vienību, lai saglabātu mikroprogrammas instrukciju secības.

4). Kas ir vadu vadība?

Vadu vadības bloks ģenerē vadības signālus, mainoties no viena stāvokļa uz citu katrā pulksteņa impulsā bez fiziskām izmaiņām ķēdē. Vadības signālu ģenerēšana ir atkarīga no instrukciju reģistra, dekodētāja un pārtraukuma signāliem.

5). Kāda ir vadības atmiņa?

Vadības ierīces informācija vai dati uz laiku vai pastāvīgi tiek glabāti vadības atmiņā.

Vadības atmiņa ir divu veidu. Tās ir brīvpiekļuves atmiņa (RAM) un tikai lasāma atmiņa (ROM).

Tādējādi tas viss attiecas uz definīciju, komponentiem, dizainu, diagrammu, funkcijām un vadības bloka veidi . Šeit ir jautājums jums: 'Kāds ir kontroles adrešu reģistra mērķis?'