Šis raksts izskaidro impulsa platuma modulācijas ģenerēšana signāli ar mainīgu darba ciklu FPGA, izmantojot VHDL. PWM ir fiksēta frekvence un mainīgs spriegums. Šajā rakstā ir apspriests arī digitālā pulksteņa pārvaldnieks, lai samazinātu pulksteņa frekvenci, samazinot pulksteņa signāla šķībumu. Fiksētu frekvenci izmanto, lai iegūtu ievaddatus, kas rada PWM signālus, izmantojot salīdzinājumu. Elektroniskie uzņēmumi izstrādā izstrādājumiem paredzēto aparatūru ar saviem standartiem un protokoliem, kas gala lietotājiem apgrūtina aparatūras pārkonfigurēšanu atbilstoši viņu vajadzībām. Šī prasība pēc aparatūras izraisīja jauna klienta konfigurējama segmenta izaugsmi lauka programmējamās integrētās shēmas, ko sauc par FPGA .

Pulsa platuma modulācija (PWM)

Pulsa platuma modulāciju plaši izmanto sakaru un vadības sistēmas . Impulsu platuma modulāciju var ģenerēt, izmantojot dažādas pieejas vadības sistēmās. Šeit, šajā rakstā, PWM tiek ģenerēts, izmantojot aparatūras apraksta valodu (VHDL) un ieviests FPGA. PWM ieviešana FPGA var ātrāk apstrādāt datus, un kontroliera arhitektūru var optimizēt telpai vai ātrumam.

PWM ir paņēmiens, kā nodrošināt loģiku “0” un loģiku “1” kontrolētā laika periodā. Tas ir signāla avots, kas ietver tā darba cikla modulāciju, lai kontrolētu slodzei nosūtītās jaudas daudzumu. PWM kvadrātveida viļņa laika periods tiek turēts nemainīgs, un tiek mainīts laiks, cik ilgi signāls paliek HIGH.

PWM ģenerē impulsus savai izejai tā, ka HIGHs un LOWs vidējā vērtība ir proporcionāla PWM ieejai. Signāla darba ciklu var mainīt. PWM signāls ir nemainīga perioda kvadrātveida vilnis ar mainīgu darba ciklu. Tas ir, PWM signāla frekvence ir nemainīga, bet signāla laika periods joprojām ir augsts un mainās, kā parādīts.

PWM signāls

VHDL

VHDL ir valoda, ko lieto, lai aprakstītu digitālo shēmu dizains . VHDL nozari un akadēmiķi izmanto digitālo shēmu simulācijas vajadzībām. Tās dizainu var simulēt un tulkot formā, kas piemērota ieviešanai aparatūrā.

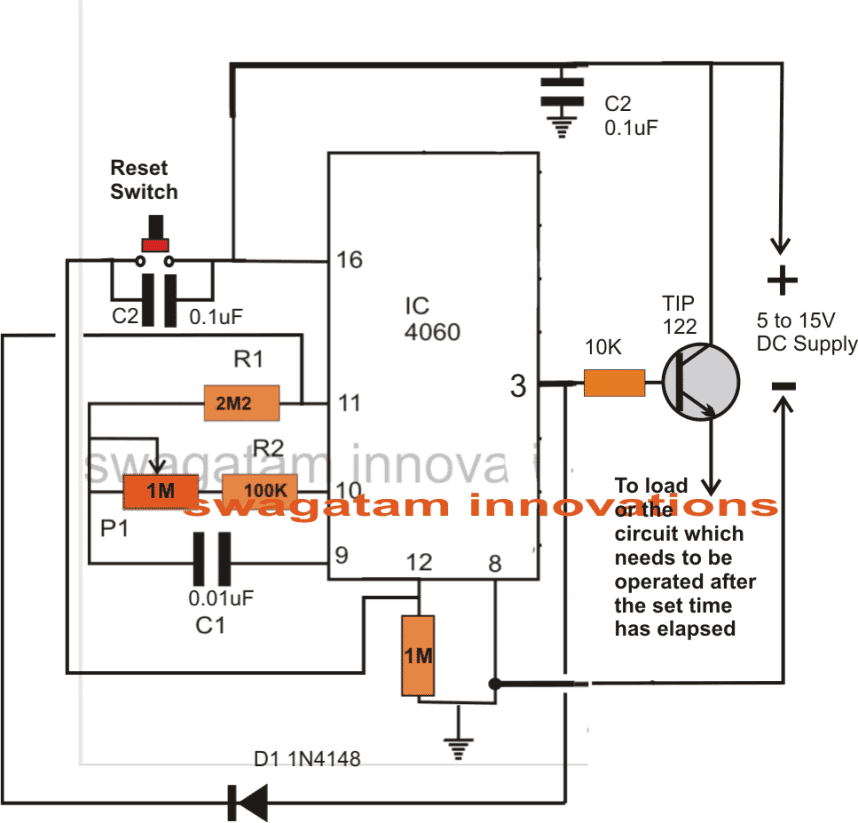

PWM arhitektūra

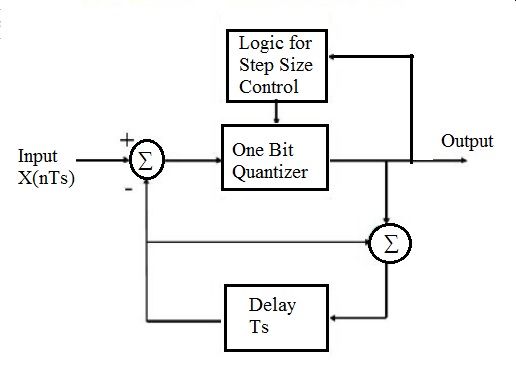

Lai izveidotu ievades datus, lai ģenerētu PWM, izmantojot ātrgaitas N bitu brīvrindas skaitītāju, kura izvadi salīdzina ar reģistra izvadi un ar salīdzinātāja palīdzību saglabā vēlamo ievades darba ciklu. Salīdzinātājs izeja ir iestatīta uz 1, ja abas šīs vērtības ir vienādas. Šo salīdzinājuma izeju izmanto, lai iestatītu RS fiksatoru. Pārplūdes signālu no skaitītāja izmanto, lai atiestatītu RS fiksatoru. The RS aizbīdņa izeja dod vēlamo PWM izvadi. Šis pārplūdes signāls tiek izmantots arī, lai reģistrā ielādētu jaunu N bitu darba ciklu. PWM ir fiksēta frekvence un mainīgs spriegums. Šī sprieguma vērtība mainās no 0V uz 5 V.

PWM signāls ar mainīgu darba ciklu

PWM pamata ģenerē signālus, kas dod PWM izvadi, ir nepieciešams salīdzinātājs, kas salīdzina divas vērtības. Pirmā vērtība apzīmē kvadrātveida signālu, ko ģenerē N bitu skaitītājs, un otrā vērtība ir kvadrātveida signāls, kas satur informāciju par darba ciklu. Skaitītājs ģenerē slodzes signālu ikreiz, kad notiek pārplūde. Kad slodzes signāls kļūst aktīvs, reģistrs ielādē jauno darba cikla vērtību. Slodzes signālu izmanto arī fiksatora atiestatīšanai. Fiksatora izeja ir PWM signāls. Tas mainās ar darba cikla vērtības izmaiņām.

Kas ir FPGA?

FPGA ir laukā programmējams vārtu masīvs. Tas ir ierīces veids, ko plaši izmanto elektroniskajās shēmās. FPGA ir pusvadītāju ierīces kas satur programmējamus loģiskos blokus un savienojuma shēmas. Pēc izgatavošanas to var ieprogrammēt vai pārprogrammēt uz nepieciešamo funkcionalitāti.

FPGA

FPGA pamati

Kad tiek ražota shēma un ja tā sastāvā ir FPGA. Tas ir ieprogrammēts ražošanas procesā, un vēlāk to var pārprogrammēt, lai izveidotu atjauninājumu vai veiktu nepieciešamās izmaiņas. Šī FPGA funkcija padara to unikālu no ASIC. Lietotnei paredzētās integrētās shēmas (ASIC) ir izgatavotas pēc pasūtījuma īpašam projektēšanas uzdevumam. Agrāk FPGA tiek izmantoti, lai izstrādātu mazu ātrumu, sarežģītību un apjoma dizainu, taču šodien FPGA viegli nospiedīs veiktspējas barjeru līdz 500MHz.

Mikrokontrolleros mikroshēma ir paredzēta klientam, un viņiem ir jāuzraksta programmatūra un jāapkopo tā hex failā, lai to ielādētu mikrokontrollerī. Šo programmatūru var viegli nomainīt, jo tā tiek glabāta zibatmiņā. FPGA nav procesora, kas darbinātu programmatūru, un ķēdi projektējam tikai mēs. Mēs varam konfigurēt FPGA tikpat vienkāršu kā AND vārti vai kompleksu kā daudzkodolu procesoru. Lai izveidotu dizainu, mēs rakstām Hardware Description Language (HDL), kas ir divu veidu - Verilog un VHDL. Tad HDL tiek sintezēts mazliet failā, izmantojot BITGEN, lai konfigurētu FPGA. FPGA saglabā konfigurāciju RAM, tas ir, konfigurācija tiek zaudēta, ja nav strāvas savienojuma. Tādējādi tie ir jākonfigurē katru reizi, kad tiek piegādāta strāva.

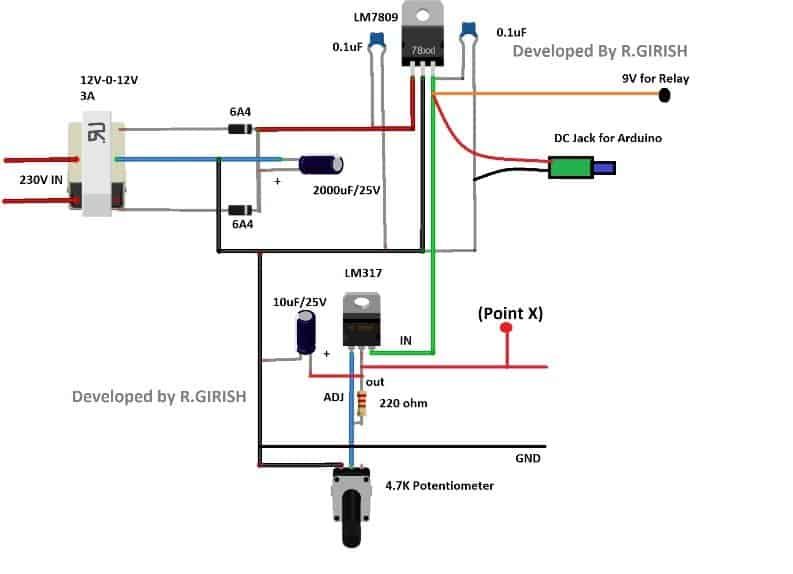

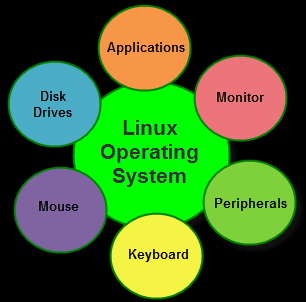

FPGA arhitektūra

FPGA ir saliekamas silīcija mikroshēmas, kuras var programmēt elektriski, lai ieviestu digitālos dizainus. Pirmo uz statisko atmiņu balstīto FPGA, ko sauc par SRAM, izmanto gan loģikas, gan starpsavienojumu konfigurēšanai, izmantojot konfigurācijas bitu plūsmu. Mūsdienu mūsdienu EPGA satur aptuveni 3 30 000 loģisko bloku un aptuveni 1100 ieejas un izejas.

FPGA arhitektūra

FPGA arhitektūra sastāv no trim galvenajiem komponentiem

- Programmējami loģikas bloki, kas realizē loģikas funkcijas

- Programmējama maršrutēšana (savieno), kas īsteno funkcijas

- I / O bloki, kurus izmanto, lai izveidotu savienojumus bez mikroshēmas

PWM signālu pielietojums

PWM signālus plaši izmanto vadības lietojumprogrammām. Tāpat kā līdzstrāvas motoru, vadības vārstu, sūkņu, hidraulikas uc vadīšana. Šeit ir daži PWM signālu pielietojumi.

- Apkures sistēmas ar lēnu laiku no 10 līdz 100Hz vai lielāku.

- Līdzstrāvas elektromotori no 5 līdz 10KHz

- Barošanas avoti vai audio pastiprinātāji no 20 līdz 200 KHz.

Šis raksts ir par PWM signālu ģenerēšana ar mainīgu darba ciklu, izmantojot FPGA. Turklāt, lai saņemtu palīdzību saistībā ar elektroniskiem projektiem vai šaubām par šo rakstu, varat sazināties ar mums, komentējot tālāk sniegto komentāru sadaļu.