Elektronikas jomā vissvarīgākais jēdziens, pie kura strādā katrs komponents, ir “ Loģikas vārti “. Tā kā loģisko vārtu jēdziens tiek ieviests visās funkcionalitātēs, piemēram, integrētajās shēmās, sensoros, komutācijas nolūkos, mikrokontrolleros un procesoros, šifrēšanas un atšifrēšanas nolūkos un citās. Papildus tam ir plašas Logic Gates lietojumprogrammas. Ir daudz loģisko vārtu veidu, piemēram, Adder, Subtractor, Full Papildinātājs , Pilnais atņemējs, Pusi atņemējs un daudzi citi. Tātad šajā rakstā ir sniegta kolektīvā informācija par puse atņemšanas ķēde , puse atņemšanas patiesības tabula , un saistītie jēdzieni.

Kas ir Half Subtractor?

Pirms dodamies apspriest pusi atņemšanas, mums jāzina binārā atņemšana. Binārā atņemšanā atņemšanas process ir līdzīgs aritmētiskajai atņemšanai. Aritmētiskajā atņemšanā tiek izmantota 2. bāzes skaitļu sistēma, savukārt binārajā atņemšanā - binārie skaitļi. Iegūtos noteikumus var apzīmēt ar starpību un aizņemties.

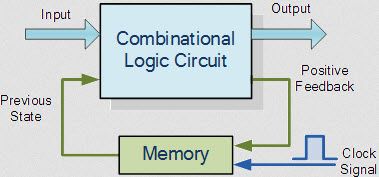

Pusi atņemējs ir vissvarīgākais kombinācijas loģikas ķēde kas tiek izmantots digitālā elektronika . Būtībā šī ir elektroniska ierīce vai citiem vārdiem sakot, mēs to varam teikt kā loģisko ķēdi. Šo shēmu izmanto, lai veiktu divu bināro ciparu atņemšanu. Iepriekšējā rakstā mēs jau esam apsprieduši pusapvienotāja un pilnas papildinātāja ķēdes jēdzieni kas aprēķinam izmanto bināros skaitļus. Līdzīgi atņemšanas ķēde atņemšanai izmanto bināros skaitļus (0,1). Pusi atņemšanas ķēdi var izveidot ar diviem loģiskie vārti, proti, NAND un EX-OR vārti . Šī shēma dod divus elementus, piemēram, starpību, kā arī to, kā viņi aizņemas.

Tāpat kā binārā atņemšanas gadījumā lielākais cipars ir 1, mēs varam ģenerēt aizņēmumu, kamēr apakšsaprotamais skaitlis 1 ir pārāks par minuend 0, un tāpēc aizņēmumam būs nepieciešams. Šis piemērs sniedz divu bināro bitu bināro atņemšanu.

Pirmais cipars | Otrais cipars | Atšķirība | Aizņemties |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Iepriekš minētajā atņemšanā abus ciparus var attēlot ar A un B. Šos divus ciparus var atņemt un iegūtos bitus norādīt kā starpību un aizņemties.

Kad mēs novērojam pirmās divas un ceturto rindu, starpība starp šīm rindām, tad atšķirība un aizņēmums ir līdzīgi, jo zemāks aizturējums ir mazāks nekā minuend. Līdzīgi, kad mēs novērojam trešo rindu, manaendes vērtība tiek atņemta no apakškontroles. Tātad atšķirība un aizņemšanās biti ir 1, jo pakārtotais cipars ir pārāks par minuend ciparu.

Šī kombinētā shēma ir būtisks līdzeklis jebkura veida digitālā shēma zināt iespējamās izejvielu un izejas kombinācijas. Piemēram, ja atņemējam ir divas ieejas, tad izejošie rezultāti būs četri. Puses atņemēja o / p ir minēts zemāk esošajā tabulā, kas apzīmēs atšķirības bitu, kā arī aizņemsies bitu. Kontūras patiesības tabulas skaidrojumu var izdarīt, izmantojot loģiskos vārtus, piemēram, EX-OR loģisko vārtu un AND vārtu darbību, kam seko NOT vārti.

Patiesības tabulas atrisināšana, izmantojot K-karte ir parādīts zemāk.

puse atņemšanas k karte

The puse atņemšanas izteiksme izmantojot patiesības tabulu un K-karti, var iegūt kā

Atšķirība (D) = ( x’y + xy ')

= x ⊕ y

Aizņemties (B) = x’y

Loģiskā ķēde

The puse atņemšanas loģiskā ķēde var izskaidrot, izmantojot loģiskos vārtus:

- 1 XOR vārti

- 1 NAV vārti

- 1 UN vārti

Pārstāvība ir

Pusi atņemšanas loģiskā shēma

Pusi atņemšanas bloka diagramma

Puses atņemšanas blokshēma ir parādīta iepriekš. Tas prasa divas ieejas, kā arī dod divas izejas. Šeit ievadi tiek attēloti ar A&B, un izejas ir atšķirība un aizņemšanās.

Iepriekš minēto shēmu var veidot ar vārtiem EX-OR & NAND. Šeit NAND vārtus var uzbūvēt, izmantojot vārdus AND un NOT. Tāpēc mums ir nepieciešami trīs loģiskie vārti, lai izveidotu pusi atņemšanas ķēdes, proti, EX-OR vārti, NOT vārti un NAND vārti.

AND un NOT vārtu kombinācija rada atšķirīgus kombinētos vārtus ar nosaukumu NAND Gate. Ex-OR vārtu izeja būs atšķirības bits un NAND vārtu izeja būs Borrow bits tām pašām ieejām A&B.

AND-Gate

AND-gate ir viena veida digitālās loģikas vārti ar vairākām ieejām un vienu izeju, un, pamatojoties uz ieeju kombinācijām, tie veiks loģisko savienojumu. Kad visas šo vārtu ieejas ir augstas, tad izeja būs augsta, pretējā gadījumā izeja būs zema. UN vārtu ar patiesības tabulu loģiskā diagramma ir parādīta zemāk.

UN Vārtu un patiesības tabula

NAV vārti

NOT vārti ir viena veida digitālās loģikas vārti ar vienu ieeju, un, pamatojoties uz ievadi, izeja tiks mainīta. Piemēram, kad NOT vārtu ieeja ir augsta, tad izeja būs zema. NOT-gate loģiskā diagramma ar patiesības tabulu ir parādīta zemāk. Izmantojot šāda veida loģiskos vārtus, mēs varam izpildīt NAND un NOR vārtus.

NAV Vārtu un patiesības tabula

Ex-OR vārti

Exclusive-OR vai EX-OR vārti ir viena veida digitālās loģikas vārti ar 2 ieejām un vienu izeju. Šo loģisko vārtu darbība ir atkarīga no vārtiem OR. Ja kāds no šo vārtu ieejām ir augsts, tad EX-OR vārtu izeja būs augsta. EX-OR simbolu un patiesības tabula ir parādīta zemāk.

XOR vārtu un patiesības tabula

Pusi atņemšanas ķēde, izmantojot Nand Gate

Projektētāju atņemšanai var veikt izmantojot loģiskos vārtus piemēram, NAND vārti un Ex-OR vārti. Lai izveidotu šo pusi atņemšanas ķēdi, mums jāzina divi jēdzieni, proti, atšķirība un aizņemšanās.

Pusi atņemšanas ķēde, izmantojot Nand Gate

Ja mēs uzraugām piesardzīgi, ir diezgan skaidrs, ka šīs ķēdes izpildītās darbības dažādība ir precīzi saistīta ar vārtu EX-OR darbību. Tāpēc, lai mainītu, mēs vienkārši varam izmantot vārtus EX-OR. Tādā pašā veidā aizņēmumu, ko rada puse papildinātāju ķēdes, var vienkārši sasniegt, izmantojot loģisko vārtu maisījumu, piemēram, AND-gate un NOT-gate.

Šo HS var projektēt arī, izmantojot NOR vārtus, kur būvniecībai nepieciešami 5 NOR vārti. Kontūras shēmas puse atņemšanas ierīce, izmantojot NOR vārtus, ir parādīta kā:

Pusi atņemējs, izmantojot Nor Gates

Patiesības tabula

Pirmais bits | Otrais bits | Atšķirība (EX-OR Out) | Aizņemties (NAND Out) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

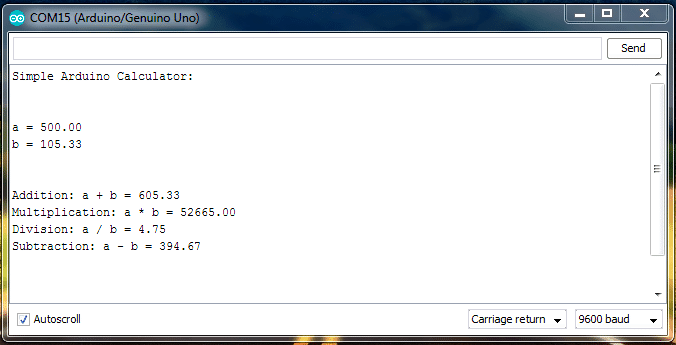

VHDL un Testbench kods

Pusi atņemšanas VHDL kods tiek izskaidrots šādi:

bibliotēka IEEE

izmantojiet IEEE.STD_LOGIC_1164.ALL

izmantojiet IEEE.STD_LOGIC_ARITH.ALL

izmantojiet IEEE.STD_LOGIC_UNSIGNED.ALL

vienība Half_Sub1 ir

Ports (a: iekš STD_LOGIC

b: STD_LOGIC

HS_Diff: out STD_LOGIC

HS_Borrow: iziet STD_LOGIC)

beigas Half_Sub1

arhitektūra Half_Sub1 uzvedība ir

sākt

HS_Diff<=a xor b

HS_Aizņemties<=(not a) and b

The testēšanas stenda kods HS ir izskaidrots šādi:

BIBLIOTĒKA IEEE

IZMANTOJIET ieee.std_logic_1164.ALL

ENTITY HS_tb IS

END HS_tb

ARHITEKTŪRA HS_tb IS_Tb

SASTĀVDAĻA HS

PORT (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

BEIGAS SASTĀVDAĻA

signāls a: std_logic: = ‘0’

signāls b: std_logic: = ‘0’

signāls HS_Diff: std_logic

signāls HS_Borrow: std_logic

SĀKT

jauns: HS PORT MAP (

a => a,

b => b,

HS_Diff => HS_Diff,

Aizņemties => aizņemties

)

stim_proc: process

sākt

uz<= ‘0’

b<= ‘0’

pagaidiet 30 ns

uz<= ‘0’

b<= ‘1’

pagaidiet 30 ns

uz<= ‘1’

b<= ‘0’

pagaidiet 30 ns

uz<= ‘1’

b<= ‘1’

pagaidi

beigu process

BEIGT

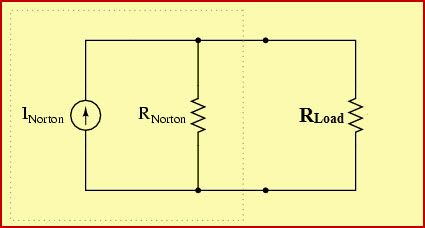

Pilnais atņemējs, izmantojot pusi atņemšanas

Pilnais atņemējs ir kombinēta ierīce, kas darbojas atņemšanas funkcionalitātē, izmantojot divus bitus, un ir manaend un subtrahend. Ķēde uzskata aizņēmumu par iepriekšējo izeju, un tai ir trīs ieejas ar divām izejām. Trīs ieejas ir manaend, subtrahend un input, kas saņemtas no iepriekšējās izejas, kas ir aizņemties, un divas izejas ir atšķirība un aizņēmums.

Pilna atņemšanas loģiskā diagramma

Patiesības tabula par pilnīgs atņemējs ir

| Ieejas | Rezultāti | |||

| X | Jā | Iņ | FS_Diff | FS_Aizņemties |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Izmantojot iepriekš minēto patiesības tabulu, zemāk ir parādīta loģiskās diagrammas reklāmu shēmu diagramma pilnā atskaitītāja ieviešanai, izmantojot pusi atņemšanas:

Pilnīgs atņemējs, izmantojot HS

Puses atņemšanas priekšrocības un ierobežojumi

Puses atņemšanas priekšrocības ir:

- Šīs ķēdes ieviešana un uzbūve ir vienkārša un vienkārša

- Šī shēma digitālā signāla apstrādē patērē minimālu jaudu

- skaitļošanas funkcijas var veikt ar uzlabotu ātruma ātrumu

Šīs kombinētās ķēdes ierobežojumi ir:

Lai gan daudzās operācijās un funkcionalitātēs ir daudz atņemēju, ir daudz ierobežojumu, un tie ir:

- Pusi atņemšanas ķēdes nepieņems “aizņemšanos” no iepriekšējām izejām, ja tas ir šīs ķēdes izšķirošais trūkums

- Tā kā daudzas reāllaika lietojumprogrammas darbojas, atņemot daudzus bitus, puse atņemšanas ierīcēs nespēj atņemt daudz bitu

Pusi apakšuzņēmēja pieteikumi

Puses atņemšanas pieteikumos ietilpst šādi.

- Pusi atņemšanas izmanto, lai samazinātu audio vai radio signālu spēku

- Tā var būt izmanto pastiprinātājos lai samazinātu skaņas traucējumus

- Puse atņemšanas ir izmanto procesora ALU

- To var izmantot, lai palielinātu un samazinātu operatorus, kā arī aprēķina adreses

- Pusi atņemšanas tiek izmantots, lai atņemtu vismazāk nozīmīgos kolonnu numurus. Daudzciparu skaitļu atņemšanai to var izmantot LSB.

Tāpēc beidzot no iepriekš minētās pusi atņemšanas teorijas mēs varam slēgt, ka, izmantojot šo shēmu, mēs varam atņemt no viena binārā bita no otra, lai nodrošinātu tādas izejas kā Atšķirība un Aizņemties. Līdzīgi mēs varam noformēt pusi atņemšanas, izmantojot NAND vārtu ķēdi, kā arī NOR vārtus. Pārējie zināmie jēdzieni ir tie, kas ir puse atņemšanas veriloga kods un kā var uzzīmēt RTL shēmu?