Šajā rakstā mēs uzzināsim, kā izveidot NOT, AND, NAND, OR un NOR loģiskos vārtus, izmantojot diskrētos tranzistorus. Galvenā tranzistoru loģisko vārtu izmantošanas priekšrocība ir tā, ka tās var darboties pat ar tik zemu spriegumu kā 1,5 V.

Dažās elektroniskās lietojumprogrammās pieejamais spriegums var būt nepietiekams, lai darbinātu TTL vai pat CMOS IC. Tas jo īpaši attiecas uz sīkrīkiem, kas darbojas ar baterijām. Bez šaubām, jums vienmēr ir 3 voltu loģiskās IC opcija. Tomēr tie ne vienmēr ir viegli pieejami entuziastam vai eksperimentētājam, un tie nedarbojas zemāk par noteiktajām sprieguma specifikācijām (parasti zem 2,5 voltiem līdzstrāvas).

Turklāt ar akumulatoru darbināmā lietojumprogrammā var būt vieta tikai vienam 1,5 voltu akumulatoram. Nu ko tad tu darīsi? Parasti IC loģikas vārti varētu aizstāt ar tranzistorizētiem loģikas vārtiem. Katram konkrētajam loģikas vārtiem parasti ir nepieciešami tikai pāris tranzistori, un tipiskai NOT vārtu invertora loģikai ir nepieciešams tikai viens tranzistors.

FET pret bipolāru tranzistoru

Lauka efekta tranzistori (FET) vs bipolāri tranzistori : kurš ir labāks variants zemsprieguma loģiskajām shēmām? Viena lieliska iezīme FAKTI ir tas, ka to 'ieslēgtā' pretestība ir neticami zema. Turklāt tiem ir nepieciešama ļoti zema ieslēgšanas strāva.

Tomēr tiem ir viens ierobežojums ļoti zema sprieguma lietojumos. Parasti vārtu sprieguma ierobežojums ir aptuveni viens volts. Turklāt pieejamais spriegums var samazināties zem FET optimālā darba diapazona, ja vārtiem ir pievienots strāvu ierobežojošs vai nolaižams rezistors.

Un otrādi, bipolāriem komutācijas tranzistoriem ir priekšrocības ārkārtīgi zema sprieguma, viena akumulatora lietojumos, jo tiem ir nepieciešami tikai 0,6–0,7 volti, lai tie ieslēgtos.

Turklāt lielākā daļa parasto FET, ko parasti pārdod burbuļu iepakojumos tuvākajā elektronikas veikalā, bieži vien ir dārgāki nekā bipolāri tranzistori. Arī bipolāro tranzistoru lielapjoma paketi parasti var iegādāties par FET pāra cenu.

FET apstrādei ir nepieciešama ievērojami lielāka piesardzība nekā bipolāro tranzistoru apstrāde. Elektrostatiskā un vispārīga eksperimentāla nepareiza izmantošana padara FET īpaši pakļautus bojājumiem. Sadegušās sastāvdaļas var sabojāt patīkamu, radošu eksperimentu vai inovāciju vakaru, neaizmirstot arī emocionālās sāpes, ko rada atkļūdošana.

Tranzistoru pārslēgšanas pamati

Šajā rakstā izskaidrotajos loģisko shēmu piemēros tiek izmantoti bipolāri NPN tranzistori, jo tie ir par pieņemamu cenu un tiem nav nepieciešama īpaša apstrāde. Lai nesabojātu ierīci vai tās daļas, kas to atbalsta, pirms ķēdes pievienošanas ir jāveic atbilstoši drošības pasākumi.

Lai gan mūsu ķēdes pārsvarā ir vērstas uz bipolārajiem savienojuma tranzistoriem (BJT), tās tikpat labi varēja konstruēt, izmantojot FET tehnoloģiju.

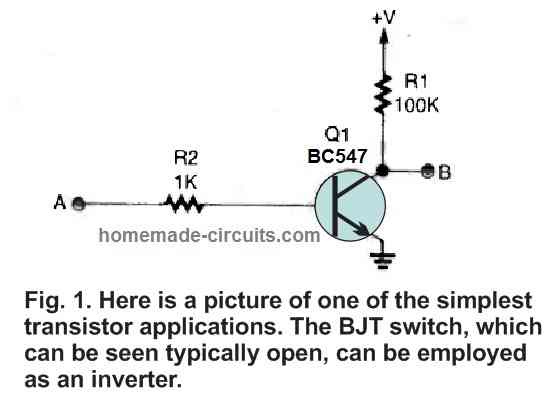

Pamata slēdža ķēde ir vienkārša tranzistora lietojumprogramma, kas ir viens no vienkāršākajiem dizainiem.

NOT vārtu izgatavošana ar vienu tranzistoru

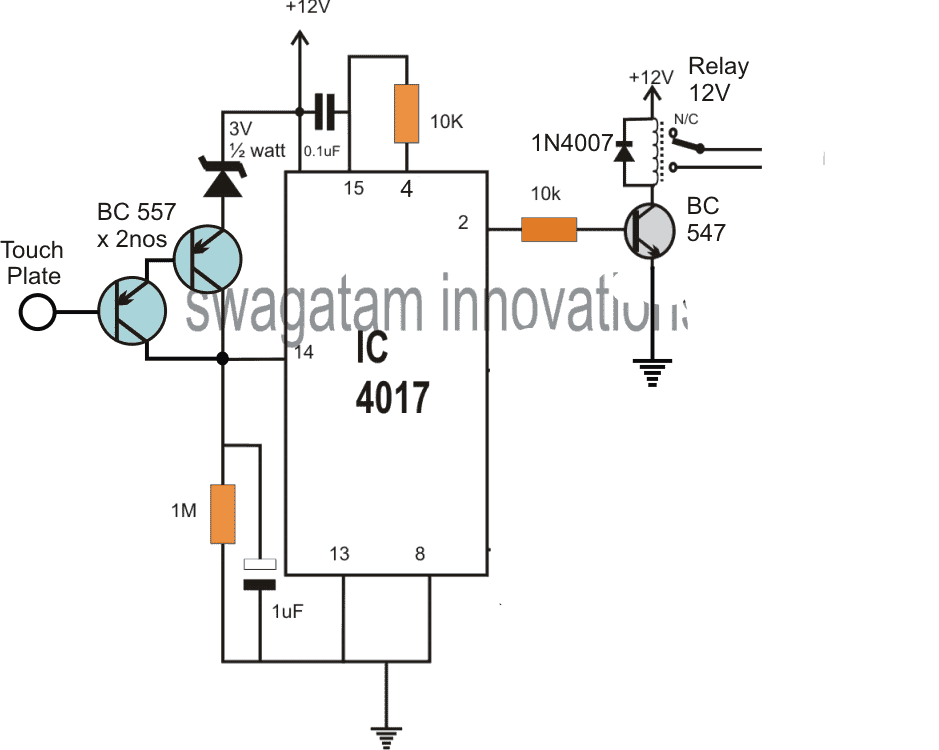

Tranzistora slēdža shēma ir parādīta 1. attēlā. Atkarībā no tā, kā tas ir ieviests konkrētā lietojumprogrammā, slēdzi var uzskatīt par zemu vai normāli atvērtu.

Vienkāršu NOT vārtu invertora loģiskos vārtus var izveidot ar vienkāršu komutācijas ķēdi, kas parādīta 1. attēlā (kur punkts A ir ieeja). NOT vārti darbojas tā, ka, ja tranzistora bāzei netiek nodrošināta līdzstrāvas nobīde (punkts A; Q1), tā paliks izslēgta, kā rezultātā izejā (vienāds ar V+ līmeni) būs augsts vai loģisks 1 (vienāds ar V+ līmeni). punkts B).

Tomēr tranzistors aktivizējas, kad Q1 bāzei tiek nodrošināta atbilstoša nobīde, nospiežot ķēdes izeju zemu vai līdz loģikai 0 (gandrīz vienāds ar nulles potenciālu). Tranzistors ar apzīmējumu Q1 ir universāls bipolārs tranzistors jeb BC547, ko parasti izmanto mazjaudas komutācijas un pastiprinātāju lietojumos.

Jebkurš tranzistors, kas ir līdzvērtīgs tam (piemēram, 2N2222, 2N4401 utt.), Derētu. R1 un R2 vērtības tika izvēlētas, lai panāktu kompromisu starp zemu strāvas aizplūšanu un saderību. Visos dizainos visi rezistori ir 1/4 vatu, 5% vienību.

Barošanas spriegums ir regulējams no 1,4 līdz 6 voltiem līdzstrāvas. Ņemiet vērā, ka ķēde var darboties kā buferis, kad slodzes rezistors un izejas savienojums tiek novirzīti uz tranzistora emitētāju.

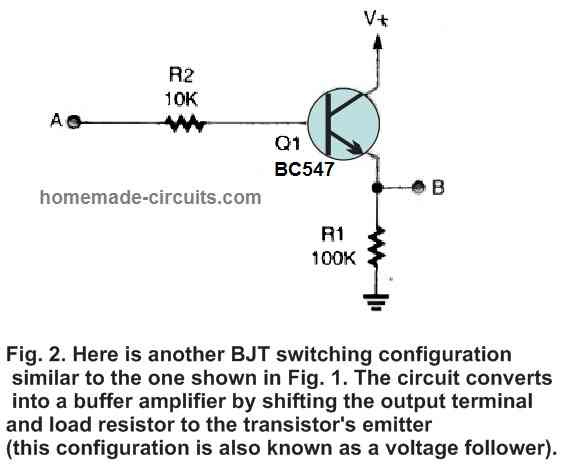

Bufera vārtu izveidošana, izmantojot vienu BC547 BJT

Sprieguma sekotājs jeb bufera pastiprinātājs ir loģiskās pārslēgšanas konfigurācijas veids, kas ir identisks 2. attēlā parādītajai. Jāņem vērā, ka slodzes rezistors un izejas spaile šajā ķēdē ir pārvietoti no tranzistora kolektora uz tā emitētāju, kas ir galvenā atšķirība starp šo dizainu un to, kas parādīts 1. attēlā.

Tranzistora darbību var arī 'apgriezt', pārvietojot slodzes rezistoru un izejas spaili uz otru BJT galu.

Citiem vārdiem sakot, ja ķēdes ieejai netiek nodrošināta novirze, ķēdes izeja paliek zema; tomēr, ja ķēdes ieejai tiek piegādāts atbilstošs spriegums, ķēdes izeja kļūst augsta. (Tas ir tieši pretējs tam, kas notiek iepriekšējā shēmā.)

Divu ieeju loģisko vārtu projektēšana, izmantojot tranzistorus

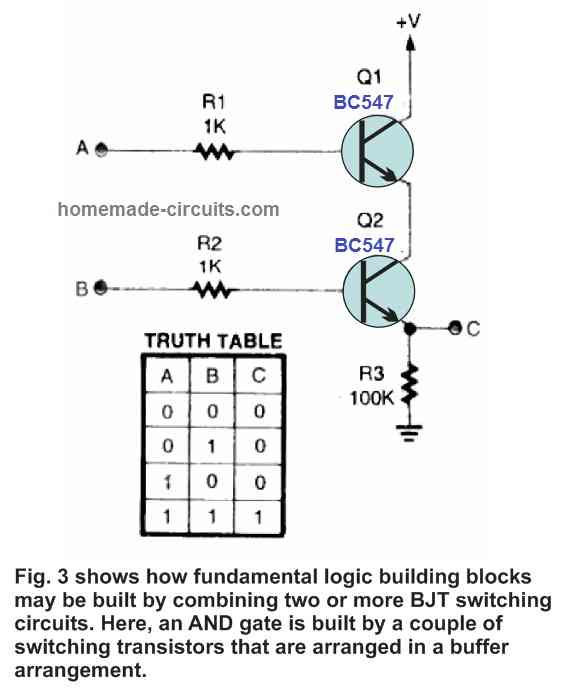

UN vārti, izmantojot divus tranzistorus

3. attēlā parādīts, kā pamata divu ieeju UN vārti var tikt izveidoti, izmantojot buferu pāri, kā arī šo vārtu patiesības tabulu. Patiesības tabula parāda, kādi izvades rezultāti būtu katrai atsevišķai ievades kopai. Punkti A un B tiek izmantoti kā ķēdes ieejas, un punkts C kalpo kā ķēdes izeja.

No patiesības tabulas ir svarīgi atzīmēt, ka tikai viena ievades parametru kopa rada loģiski augstu izejas signālu, bet visas pārējās ievades kombinācijas rada loģiski zemu izvadi. UN vārtu izeja 3. attēlā paliek nedaudz zem V+, tiklīdz tā kļūst augsta.

Tas notiek sprieguma krituma dēļ starp diviem tranzistoriem (Q1 un Q2).

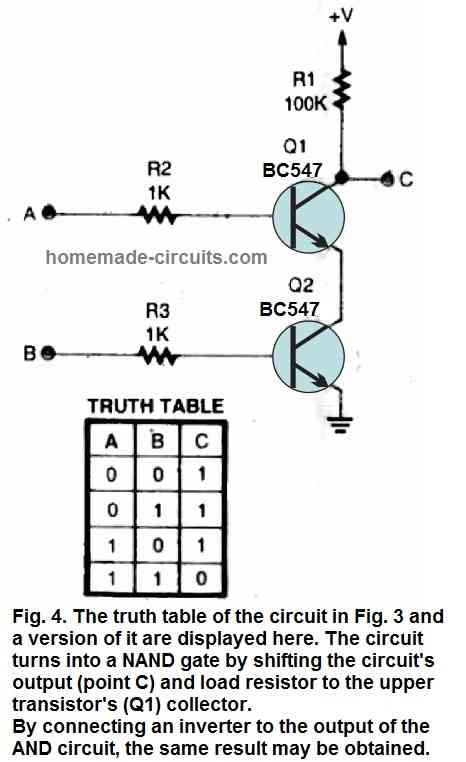

NAND vārti, izmantojot divus tranzistorus

Cits shēmas variants 3. attēlā un saistītā patiesības tabula ir parādīts 4. attēlā. Ķēde pārvēršas par NAND vārtiem, novirzot izeju (punkts C) un izejas rezistoru uz augšējā tranzistora (Q1) kolektoru.

Tā kā gan Q1, gan Q2 ir jāieslēdz, lai novilktu R1 apakšējo pusi uz zemi, sprieguma zudums pie izejas C ir nenozīmīgs.

Ja tranzistora UN vai tranzistora NAND vārtiem ir vajadzīgas vairāk nekā divas ieejas, parādītajos dizainos var pieslēgt vairāk tranzistoru, lai nodrošinātu trīs, četrus utt. ieejas UN vai NAND vārtus.

Taču, lai kompensētu atsevišķo tranzistoru sprieguma zudumus, attiecīgi jāpalielina V+.

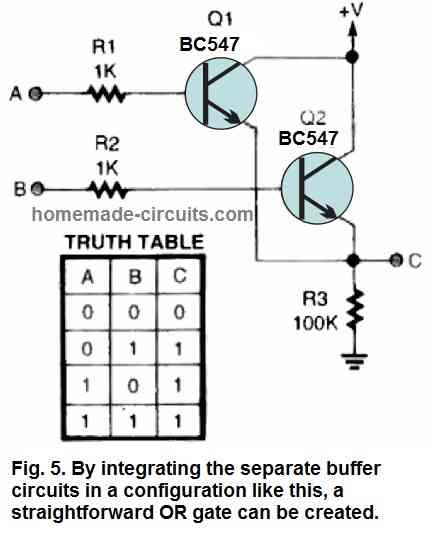

VAI Vārti, izmantojot divus tranzistorus

Cits loģiskās shēmas veids ar divām ieejām ir redzams 5. attēlā kopā ar VAI vārtu ķēdes patiesības tabulu.

Ķēdes izeja ir augsta, ja ieeja A vai ieeja B tiek nospiesta augstu, tomēr kaskādes tranzistoru dēļ sprieguma kritums pārsniedz 0,5 voltus. Vēlreiz parādītie skaitļi norāda, ka ir pietiekami daudz sprieguma un strāvas, lai darbinātu nākamos tranzistora vārtus.

NOR vārti, izmantojot divus tranzistorus

6. attēlā ir parādīti nākamie vārti mūsu sarakstā, divu ieeju NOR vārti, kopā ar to patiesības tabulu. Līdzīgi kā UN un NAND vārti reaģē viens uz otru, VAI un NOR ķēdes dara to pašu.

Katrs no parādītajiem vārtiem spēj nodrošināt pietiekami daudz piedziņas, lai aktivizētu vismaz vienu vai vairākus blakus esošos tranzistora vārtus.

Tranzistoru loģikas vārtu lietojumprogrammas

Ko jūs darāt ar iepriekš izskaidrotajām digitālajām shēmām, kuras jums tagad pieder? Jebkas, ko jūs varētu paveikt ar parastajiem TTL vai CMOS vārtiem, taču neuztraucoties par barošanas sprieguma ierobežojumiem. Šeit ir daži tranzistora loģisko vārtu lietojumi darbībā.

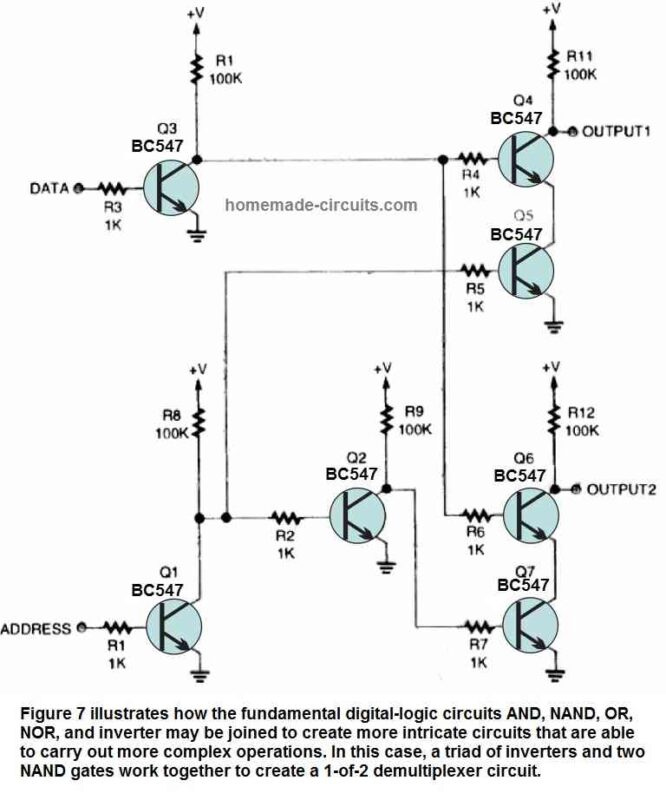

Demultipleksera ķēde

1-of-2 demultiplekseris ar trim NOT vārtiem un divām NAND shēmām ir redzams 7. attēlā. Atbilstošā izeja tiek izvēlēta, izmantojot viena bita 'adreses ievadi', kas var būt OUTPUT1 vai OUTPUT2, kamēr tiek lietota braukšanas informācija. ķēdē, izmantojot DATA ieeju.

Ķēde darbojas visefektīvāk, ja datu pārraides ātrums tiek uzturēts zem 10 kHz. Ķēdes funkcionalitāte ir vienkārša. DATA ieeja tiek piegādāta ar nepieciešamo signālu, kas ieslēdz Q3 un invertē Q3 kolektorā ienākošos datus.

Q1 izeja tiek virzīta uz augstu, ja ADDRESS ieeja ir zema (iezemēta vai netiek nodrošināts signāls). Q1 kolektorā augstā jauda ir sadalīta divos veidos. Pirmajā ceļā Q1 izeja tiek piegādāta Q5 bāzei (vienai no divu ieeju NAND vārtu kājām), ieslēdzot to un tādējādi 'aktivizējot' NAND vārtus, kas sastāv no Q4 un Q5.

Otrajā ceļā Q1 augstā izvade vienlaikus tiek ievadīta cita NOT vārtu (Q2) ieejā. Pēc dubultās inversijas Q2 izlaide kļūst zema. Šis zemais tiek piegādāts Q7 bāzei (viens otrā NAND vārtu terminālis, kas sastāv no Q6 un Q7), tādējādi izslēdzot NAND ķēdi.

Šādos apstākļos jebkura informācija vai signāls, kas tiek pievienots DATA ieejai, nonāk OUTPUT1. Alternatīvi, situācija tiek mainīta, ja ievadei ADRESE tiek dots augsts signāls. Tas nozīmē, ka visa shēmai sniegtā informācija tiks rādīta izejā OUTPUT2, jo Q4/Q5 NAND vārti ir atspējoti un Q6/Q7 NAND vārti ir iespējoti.

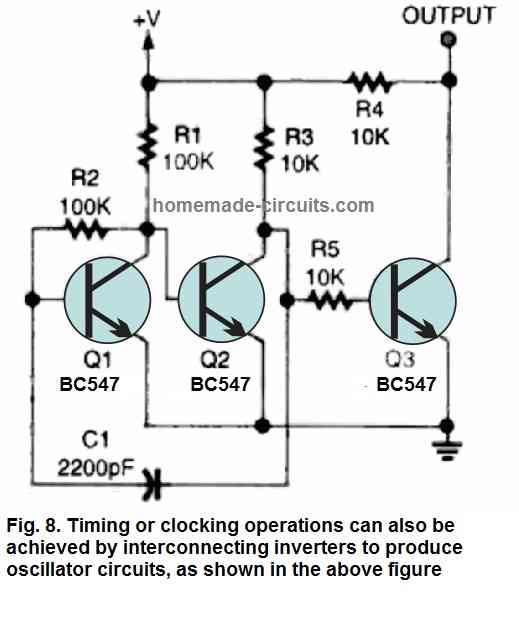

Oscilatora ķēde (pulksteņa ģenerators)

Mūsu nākamā tranzistora loģikas vārstu lietojumprogramma, kas parādīta 8. attēlā, ir pamata pulksteņa ģenerators (pazīstams arī kā oscilators), kas izgatavots no trim parastiem NOT vārtiem pārveidotājiem (viens no tiem ir nobīdīts, izmantojot atgriezeniskās saites rezistoru R2, kas to ievieto analogais reģions).

Lai izlīdzinātu izvadi, ir iekļauts trešais NOT vārti (Q3), kas nodrošina oscilatora izejas papildinājumu. C1 vērtību var palielināt vai samazināt, lai mainītu ķēdes darbības frekvenci. Izejas viļņu formas frekvence ir aptuveni 7 kHz ar V+ pie 1,5 voltu līdzstrāvas, izmantojot norādītās komponentu vērtības.

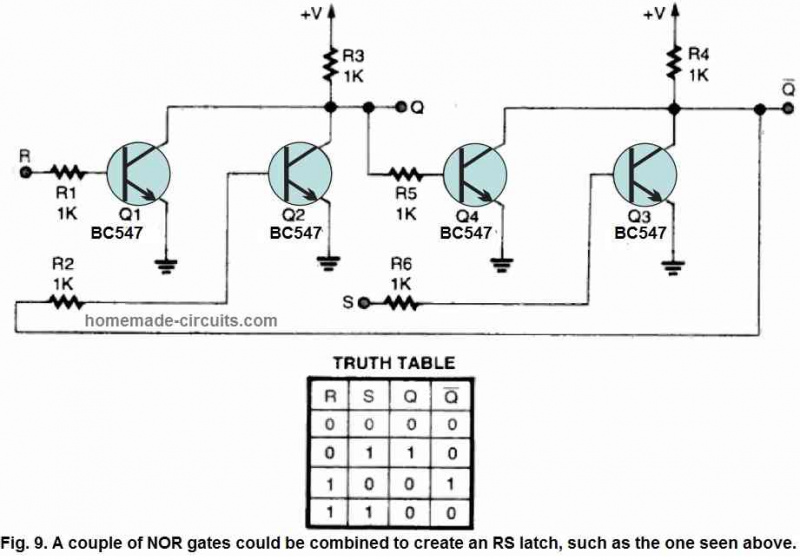

RS fiksatora ķēde

9. attēlā parādīta mūsu galīgā pielietojuma shēma, RS fiksators, kas sastāv no diviem NOR vārtiem. Lai nodrošinātu veselīgu izejas piedziņu pie Q un Q izejām, rezistori R3 un R4 ir noregulēti uz 1k omi.

RS fiksatora patiesības tabula tiek parādīta līdzās shematiskajam dizainam. Šie ir tikai daži ilustrācijas no vairākām uzticamām zemsprieguma digitālajām loģisko vārtu shēmām, kuras var izveidot, izmantojot atsevišķus tranzistorus.

Shēmām, kurās izmanto tranzistorizētu loģiku, ir nepieciešams pārāk daudz detaļu

Daudzas problēmas var atrisināt, izmantojot visas šīs zemsprieguma tranzistorizētās loģiskās shēmas. Tomēr pārāk daudzu šo tranzistorizēto vārtu izmantošana var radīt jaunas problēmas.

Tranzistoru un rezistoru skaits var kļūt diezgan liels, ja jūsu veidotajā lietojumprogrammā ir daudz vārtu, kas aizņem vērtīgu vietu.

Viens no veidiem, kā atrisināt šo problēmu, ir izmantot tranzistoru blokus (daudzi tranzistori ir iesaiņoti plastmasā) un SIP (Single Inline Package) rezistoru izmantošana atsevišķu vienību vietā.

Iepriekš minētā pieeja var ietaupīt tonnu vietas uz PCB, vienlaikus saglabājot veiktspēju, kas ir līdzvērtīga to pilna izmēra ekvivalentu veiktspējai. Tranzistoru bloki tiek piedāvāti ar virsmas montāžu, 14 kontaktu caurumu un četrpakojuma iepakojumu.

Lielākajai daļai shēmu tranzistoru veidu sajaukšana var būt diezgan pieņemama.

Tomēr ir ieteicams, lai eksperimentētājs strādātu ar viena veida tranzistoru, lai izveidotu tranzistorizētās loģiskās shēmas (tas nozīmē, ja izveidojat vārtu sekciju, izmantojot BC547, tad mēģiniet izmantot to pašu BJT arī pārējo atlikušo vārtu izveidošanai).

Iemesls ir tāds, ka dažādiem tranzistoru variantiem var būt nedaudz atšķirīgas īpašības un tādējādi tie var darboties atšķirīgi.

Piemēram, dažiem tranzistoriem bāzes ieslēgšanās ierobežojums var būt lielāks vai mazāks nekā citam, vai arī kopējais strāvas pastiprinājums var būt nedaudz lielāks vai mazāks.

No otras puses, viena veida tranzistora lielapjoma kastes iegādes izmaksas varētu būt arī zemākas. Jūsu ķēžu veiktspēja uzlabosies, ja jūsu loģiskie vārti tiks veidoti, izmantojot atbilstošus tranzistorus, un projekts kopumā galu galā būs izdevīgāks.