Instrukciju kopa vai instrukciju kopas arhitektūra ir tā datora struktūra, kas nodrošina datoram komandas, kas vada datoru apstrādāt datus. Instrukciju komplekts sastāv no instrukcijām, adresēšanas režīmiem, vietējiem datu tipiem, reģistriem, pārtraukumiem, izņēmumu apstrādes un atmiņas arhitektūras. Instrukciju kopu var atdarināt programmatūrā, izmantojot tulku, vai iebūvēt procesora aparatūrā. Instrukciju kopas arhitektūru var uzskatīt par robežu starp programmatūru un aparatūru. Mikrokontrolleru klasifikācija un mikroprocesorus var veikt, pamatojoties uz RISC un CISC instrukciju kopas arhitektūru.

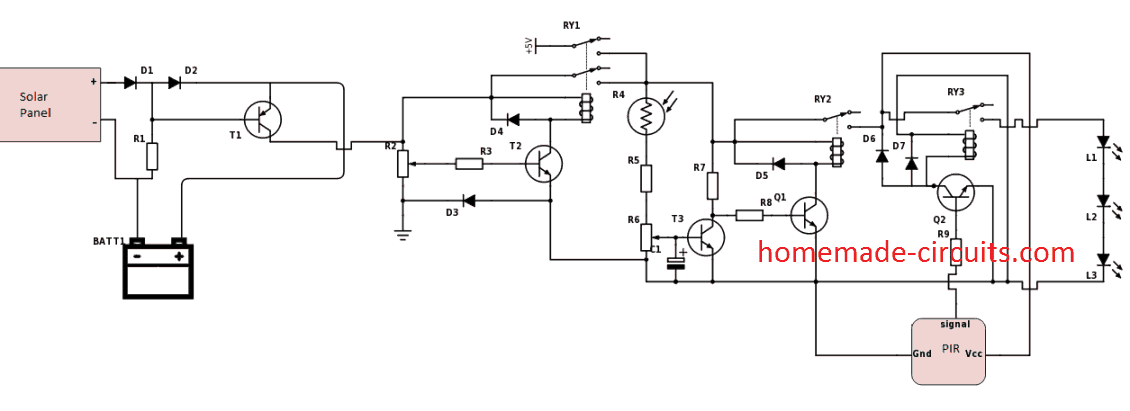

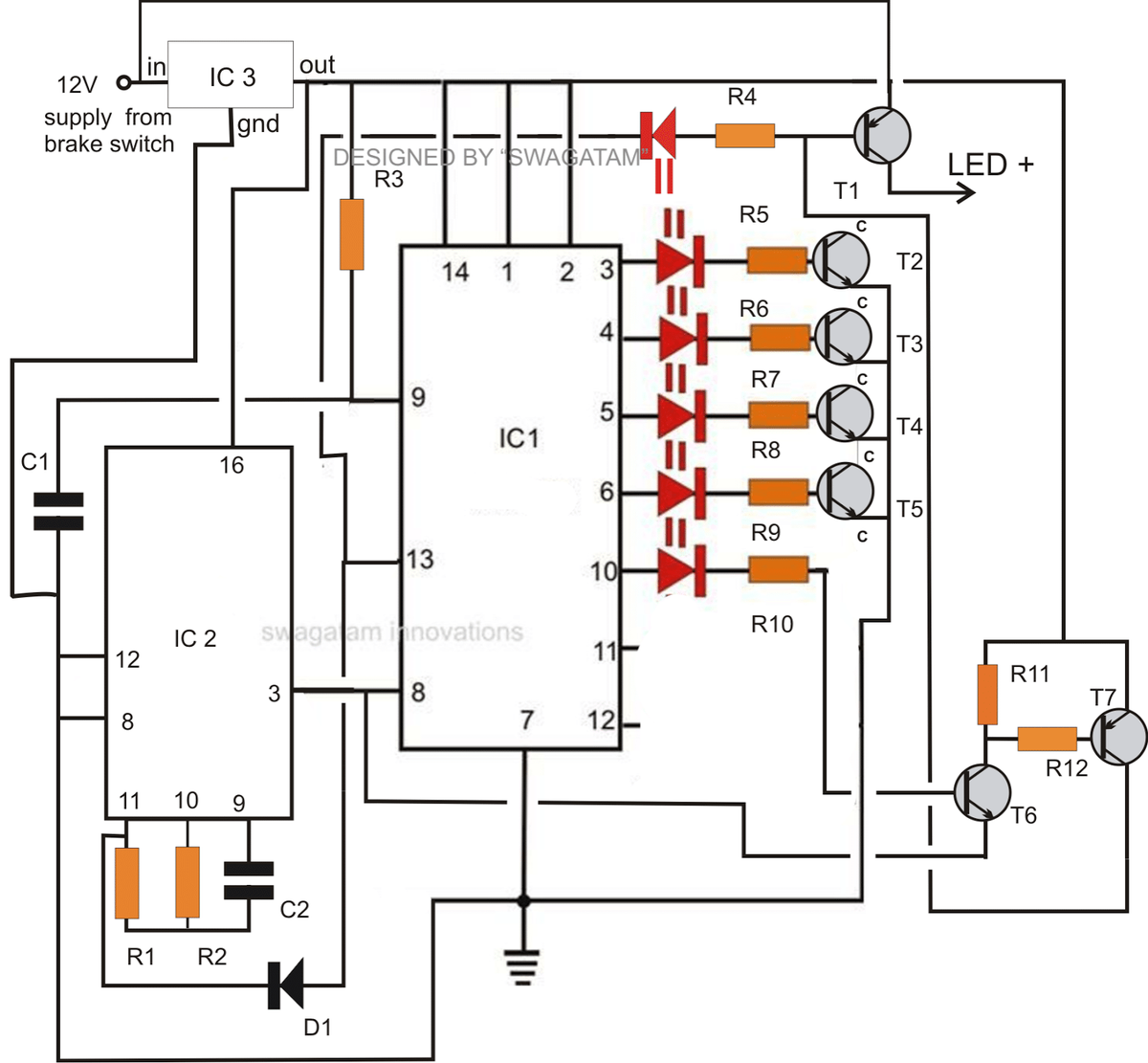

Procesora instrukciju kopa

Instrukciju kopa norāda procesora funkcionalitāti, ieskaitot procesora atbalstītās darbības, procesora glabāšanas mehānismus un programmu sastādīšanas veidu procesoram.

Kas ir RISC un CISC?

The RISC un CISC var paplašināt šādi:

RISC apzīmē samazināto instrukciju kopas datoru un

CISC ir komplekso instrukciju komplekta dators.

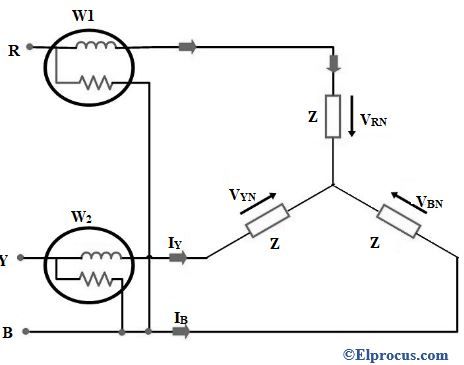

RISC (Reduced Instruction Set Computer) arhitektūra

RISC arhitektūra

The mikrokontrolleru arhitektūra kas izmanto nelielu un ļoti optimizētu instrukciju kopu, sauc par Reduced Instruction Set Computer vai vienkārši sauktu par RISC. To sauc arī par LOAD / STORE arhitektūru.

70. gadu beigās un 80. gadu sākumā RISC projektus galvenokārt izstrādāja Stanforda, UC-Berkley un IBM. Džons Koks no IBM pētnieku grupas izstrādāja RISC, samazinot instrukciju skaitu, kas nepieciešami aprēķinu apstrādei ātrāk nekā CISC. RISC arhitektūra ir ātrāka, un mikroshēmas, kas nepieciešamas RISC arhitektūras ražošanai, arī ir lētākas, salīdzinot ar CISC arhitektūru.

RISC arhitektūras raksturīgās iezīmes

- RISC cauruļvadu tehnoloģija vienlaikus izpilda vairākas instrukciju daļas vai posmus tā, lai katra CPU instrukcija tiktu optimizēta. Tādējādi RISC procesoriem ir Pulkstenis vienā instrukcijā viens cikls, un to sauc par viena cikla izpildi.

- Tas optimizē reģistra izmantošana ar lielāku reģistru skaitu RISC un lielāku mijiedarbību skaitu atmiņā var novērst.

- Vienkāršus adresēšanas režīmus, pat sarežģītu adresēšanu var veikt, izmantojot aritmētiku UN / VAI loģiskas darbības .

- Tas vienkāršo kompilatora dizainu, izmantojot identiskus vispārējas nozīmes reģistrus, kas ļauj jebkuru reģistru izmantot jebkurā kontekstā.

- Lai efektīvi izmantotu reģistrus un optimizētu cauruļvadu izmantošanu, ir nepieciešams samazināt instrukciju kopu.

- Tiek samazināts opkodam izmantoto bitu skaits.

- Kopumā RISC ir 32 vai vairāk reģistru.

RISC procesora arhitektūras priekšrocības

- Tā kā RISC ir mazs instrukciju kopums, augsta līmeņa valodu kompilatori var izveidot efektīvāku kodu.

- RISC ļauj brīvi izmantot vietu mikroprocesori tā vienkāršības dēļ.

- Tā vietā, lai izmantotu Stack, daudzi RISC procesori izmanto reģistrus argumentu nodošanai un lokālo mainīgo turēšanai.

- RISC funkcijās tiek izmantoti tikai daži parametri, un RISC procesori nevar izmantot izsaukuma instrukcijas, tāpēc izmanto fiksēta garuma instrukcijas, kuras ir viegli sagatavot cauruļvadam.

- Operācijas ātrumu var palielināt un izpildes laiku samazināt līdz minimumam.

- Nepieciešams ļoti mazs komandu formātu skaits (mazāk nekā četri), daži instrukciju skaits (aptuveni 150) un daži adresēšanas režīmi (mazāk nekā četri).

RISC procesora arhitektūras trūkumi

- Palielinoties instrukciju garumam, RISC procesoriem kļūst sarežģītāk izpildīt, jo tā rakstzīmju cikls katrai instrukcijai.

- RISC procesoru veiktspēja lielākoties ir atkarīga no sastādītāja vai programmētāja, jo galvenā loma ir kompilatora zināšanām, savukārt CISC koda pārveidošana par RISC kodu tādējādi ģenerētā koda kvalitāte ir atkarīga no sastādītāja.

- CISC koda pārcelšana uz RISC kodu, ko sauc par koda paplašināšanu, palielinās izmēru. Šīs koda paplašināšanas kvalitāte atkal būs atkarīga no kompilatora un arī no mašīnas instrukciju kopas.

- RISC procesoru pirmā līmeņa kešatmiņa ir arī RISC trūkums, kurā šiem procesoriem ir lielas atmiņas kešatmiņas pašā mikroshēmā. Norādījumu barošanai tie prasa ļoti daudz ātrās atmiņas sistēmas .

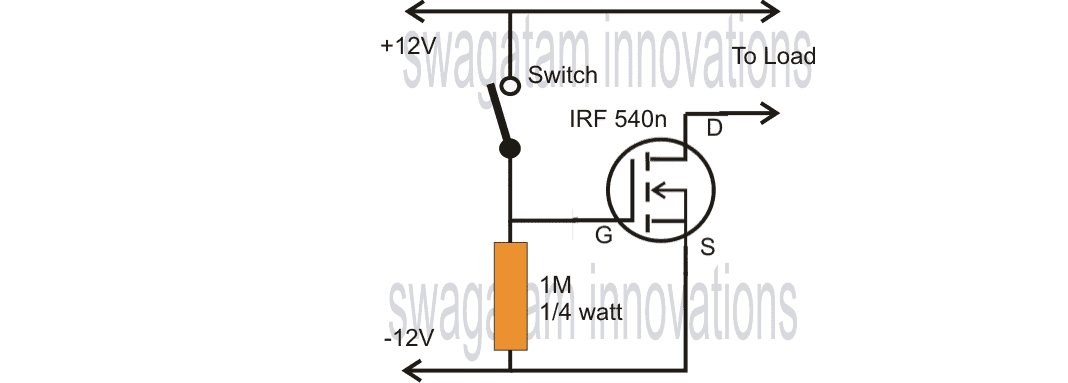

CISC (Complex Instruction Set Computer) arhitektūra

Galvenais CISC procesora arhitektūras mērķis ir pabeigt uzdevumu, izmantojot mazāku montāžas līniju skaitu. Šim nolūkam procesors ir izveidots, lai veiktu virkni darbību. Sarežģītu instrukciju sauc arī par MULT, kas darbojas atmiņas bankas tieši, neliekot kompilatoram veikt glabāšanas un ielādes funkcijas.

CISC arhitektūra

CISC arhitektūras iezīmes

- Lai vienkāršotu datora arhitektūru, CISC atbalsta mikroprogrammēšanu.

- CISC ir vairāk iepriekš definētu instrukciju, kas padara augsta līmeņa valodas viegli izstrādājamas un īstenojamas.

- CISC sastāv no mazāka reģistru skaita un lielāka adresēšanas režīmu skaita, parasti no 5 līdz 20.

- CISC procesors instrukciju izpildei prasa dažādu ciklu laiku - vairāku pulksteņu ciklus.

- CISC sarežģīto instrukciju komplekta dēļ cauruļvadu izgatavošanas tehnika ir ļoti sarežģīta.

- CISC sastāv no vairākiem norādījumiem, parasti no 100 līdz 250.

- Īpaši norādījumi tiek izmantoti ļoti reti.

- Atmiņā esošos operandus manipulē ar instrukcijām.

CISC arhitektūras priekšrocības

- Katra mašīnvalodas instrukcija tiek sagrupēta mikrokoda instrukcijā un attiecīgi izpildīta, un pēc tam tiek glabāta iebūvēta galvenā procesora atmiņā, saukta par mikrokoda ieviešanu.

- Tā kā mikrokoda atmiņa ir ātrāka nekā galvenā atmiņa, mikrokoda instrukciju kopu var ieviest, bez ievērojamas ātruma samazināšanas salīdzinājumā ar vadu vadu.

- Pilnīgi jaunu instrukciju kopu var apstrādāt, modificējot mikroprogrammas dizainu.

- CISC, programmas ieviešanai nepieciešamo instrukciju skaitu var samazināt, izveidojot bagātīgas instrukciju kopas, kā arī var likt efektīvāk izmantot lēno galveno atmiņu.

- Sakarā ar lielāko instrukciju kopu, kas sastāv no visām iepriekšējām instrukcijām, tas atvieglo mikrokodēšanu.

CISC trūkumi

- Pulksteņa laika daudzums, kas tiek veikts ar dažādām instrukcijām, būs atšķirīgs - tāpēc mašīnas darbība palēninās.

- Instrukciju kopas sarežģītība un mikroshēmas aparatūra palielinās, jo katra jaunā procesora versija sastāv no iepriekšējo paaudžu apakškopas.

- Tikai 20% esošo instrukciju tiek izmantotas tipiskā programmēšanas pasākumā, kaut arī pastāv daudzas specializētas instrukcijas, kuras pat netiek bieži izmantotas.

- Nosacījuma kodus nosaka CISC instrukcijas kā blakus efektu katrai instrukcijai, kas prasa laiku šim iestatījumam - un, tā kā nākamā instrukcija maina nosacījuma koda bitus, kompilatoram ir jāpārbauda nosacījuma koda biti, pirms tas notiek.

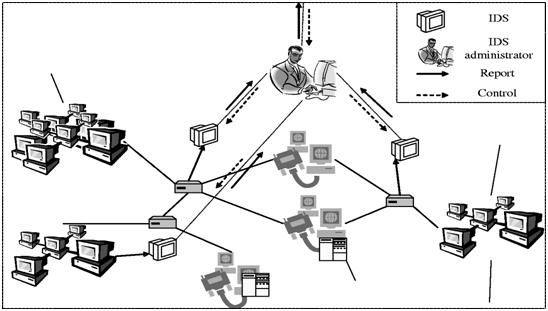

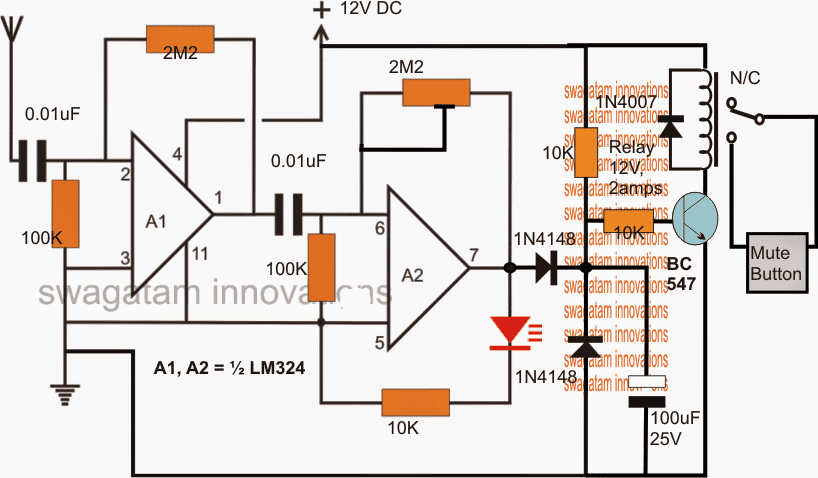

RISC Vs. CISC

- Programmētājs var novērst izšķērdēšanas ciklus, noņemot nevajadzīgo kodu RISC, taču, izmantojot CISC kodu, CISC neefektivitātes dēļ tiek izšķērdēti cikli.

- RISC katra instrukcija ir paredzēta neliela uzdevuma izpildei tā, ka, lai veiktu sarežģītu uzdevumu, kopā tiek izmantotas vairākas mazas instrukcijas, turpretī, lai veiktu vienu un to pašu uzdevumu, izmantojot CISC, ir nepieciešami tikai daži norādījumi - jo tas spēj veikt sarežģītu uzdevumu jo instrukcijas ir līdzīgas augstas valodas kodam.

- CISC parasti izmanto datoriem, savukārt RISC - viedtālruņiem, planšetdatoriem un citām elektroniskām ierīcēm.

Šis attēls parāda vairāk atšķirību starp RISC un CISC

RISC Vs. CISC

Tādējādi šajā rakstā par īsu ideju tiek aplūkotas RISC un CISC arhitektūras iezīmes, kas raksturīgas RISC un CISC procesoru arhitektūras priekšrocībām un trūkumiem, kā arī atšķirības starp RISC un CISC arhitektūrām. Lai iegūtu vairāk informācijas par RISC un CISC arhitektūru, lūdzu, ievietojiet savus jautājumus, komentējot tālāk.

Foto kredīti:

- Procesora instrukciju kopa arstechnica

- RISC arhitektūra lsi-konkurss

- RISC pret CISC līdz csar piešķiršana