Šī piedāvātā 4kva pirmā daļa ir sinhronizēta sakraujama invertora shēma tiek apspriests, kā ieviest izšķirošo automātisko sinhronizāciju četros invertoros attiecībā uz frekvenci, fāzi un spriegumu, lai invertori darbotos neatkarīgi viens no otra, tomēr panākot izeju, kas ir vienāda ar otru.

Ideju pieprasīja Dāvida kungs. Šajā e-pasta sarunā starp viņu un mani ir sīki aprakstītas ierosinātās sinhronizētās 4kva sakraujošās invertora shēmas galvenās specifikācijas.

1. e-pasts

Sveiks, Svagatam,

Pirmkārt, es gribēju pateikt paldies par jūsu ieguldījumu pasaulē kopumā, informācija un vissvarīgāk par jūsu vēlmi dalīties savās zināšanās, lai palīdzētu citiem cilvēkiem, manuprāt, ir nenovērtējama daudzu iemeslu dēļ.

Es vēlētos uzlabot dažas jūsu kopīgotās shēmas, lai tās atbilstu maniem mērķiem, diemžēl, lai gan es saprotu, kas notiek ķēdēs, man trūkst radošuma un zināšanu, lai pats veiktu grozījumus.

Es parasti varu sekot ķēdēm, ja tās ir mazas, un es redzu, kur tās pievienojas / savienojas ar lielākām shēmām.

Ja es vēlētos, es vēlētos mēģināt izskaidrot, ko es vēlētos sasniegt, lai gan man nav ilūziju, ka jūs esat ļoti aizņemts cilvēks un nevēlaties nevajadzīgi aizņemt jūsu dārgo laiku.

Galīgais mērķis būtu tāds, ka es vēlētos uzbūvēt (salikt komponentus) daudzu avotu atjaunojamās enerģijas mikrotīklu, izmantojot Solar PV, Windmills un biodīzeļa ģeneratorus.

Pirmais solis ir PV saules invertora uzlabojumi.

Es gribētu izmantot jūsu 48 voltu tīra sinusa viļņu invertora ķēdi, kas spēj uzturēt nemainīgu 2kW 230V izeju, tai jāspēj vismaz 3 reizes pārsniegt šo jaudu ļoti īsā laikā.

Galvenā modifikācija, kuru es vēlos to panākt, lai izveidotu vairākas šīs invertoru vienības, kas darbotos paralēli un savienotas ar maiņstrāvas kopnes joslu.

Es gribētu, lai katrs invertors neatkarīgi un pastāvīgi ņemtu maiņstrāvas kopnes joslas frekvenci, spriegumu un strāvu (slodzi).

Es nosaukšu šos invertorus par vergu vienībām.

Ideja, kas ir invertmoduļi, būs “plug and play”.

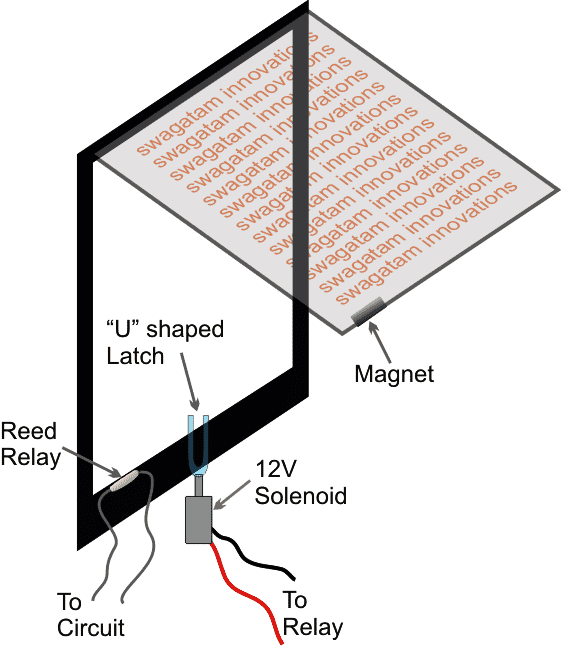

Kad invertors, kad tas ir pievienots maiņstrāvas kopnes joslai, pastāvīgi atlasa / mēra frekvenci maiņstrāvas kopnes joslā un izmanto šo informāciju, lai vadītu 4047 IC ieeju tā, lai tā pulksteņa izvadi varētu uzlabot vai palēnināt, līdz tas precīzi klonē frekvenci maiņstrāvas kopnes josla, kad abas viļņu formas ir sinhronizētas, invertors aizvērs kontaktoru vai releju, kas savieno invertēšanas izejas posmu ar maiņstrāvas kopnes joslu.

Gadījumā, ja frekvence uz stieņa vai spriegums pārvietojas ārpus iepriekš noteiktās pielaides, invertora modulim jāatver izejas pakāpes relejs vai kontaktors, efektīvi atvienojot invertora izejas posmu no maiņstrāvas joslas, lai aizsargātu sevi.

Pēc tam, kad tie ir savienoti ar maiņstrāvas kopnes joslu, vergu vienības gulēs miegā vai vismaz invertora izejas pakāpe gulēs, kamēr joslas slodze ir mazāka par visu pakārtoto invertoru summu. Iedomājieties, vai pie maiņstrāvas kopnes joslas ir piestiprināti 3 vergu invertori, tomēr joslas slodze ir tikai 1,8 kW, tad pārējie divi vergi gulētu gulēt.

Abpusējs arī būtu taisnība, ka, ja slodze uz stieņa lēktu, sakot, 3kW, viens no gulēšanas invertiem uzreiz pamodīsies (jau būs sinhronizēts), lai piegādātu papildus nepieciešamo enerģiju.

Es domāju, ka daži lieli kondensatori katrā izejas posmā piegādā nepieciešamo enerģiju, kamēr invertoram ir ļoti īss brīdis, kamēr tas pamostas.

Būtu vēlams (tikai pēc manām domām) nevis tieši savienot katru invertoru ar otru, bet gan, ka tie ir neatkarīgi autonomi.

Es vēlos mēģināt izvairīties no mikrokontrolleriem vai vienību kļūdām vai defektiem, pārbaudot viens otru vai vienības, kurām sistēmā ir “adrese”.

Domās iedomājos, ka pirmā maiņstrāvas kopnes joslā pirmā pievienotā ierīce būtu ļoti stabils atsauces invertors, kas ir pastāvīgi savienots.

Šis atsauces invertors nodrošinās frekvenci un spriegumu, ko citas vergu vienības izmantotu, lai izveidotu savas attiecīgās izejas.

Diemžēl es nevaru apdomāt, kā jūs varētu novērst atgriezenisko saiti, kur vergu vienības katra varētu kļūt par atskaites vienību.

Ārpus šī e-pasta ziņojuma man ir daži mazi ģeneratori, kurus es vēlētos savienot ar maiņstrāvas kopnes joslu, sinhronizējot ar atsauces invertoru, lai piegādātu enerģiju gadījumā, ja slodze pārsniedz DC max izejas jaudu.

Kopējais pieņēmums ir tāds, ka maiņstrāvas kopnes joslai uzrādītā slodze nosaka, cik daudz invertoru un galu galā cik ģeneratoru vai nu autonomi pieslēgs, vai atvienos, lai apmierinātu pieprasījumu, jo tas, cerams, ietaupītu enerģiju vai vismaz netērētu enerģiju.

Sistēma, kas pilnībā veidota no vairākiem moduļiem, būtu paplašināma / savietojama, kā arī izturīga / izturīga tā, ka, ja kāds vai varbūt divas vienības neizdotos, sistēma turpinātu darboties, neatkarīgi no tā, vai tā ir ar samazinātu jaudu.

Esmu pievienojis blokshēmu un pagaidām izslēdzis akumulatora uzlādi.

Es plānoju uzlādēt akumulatora banku no maiņstrāvas kopnes un izlīdzināt līdz 48 V līdzstrāvai līdzšinējā strāvā, tādā veidā es varu uzlādēt no ģeneratoriem vai atjaunojamiem enerģijas avotiem, es apzinos, ka tas, iespējams, nav tik efektīvs kā DC mppt izmantošana, bet es domāju, ko es zaudēt efektivitāti es iegūt elastību. Es dzīvoju tālu no pilsētas vai komunālā tīkla.

Atsaucei uz maiņstrāvas kopnes joslu būtu jābūt minimālai pastāvīgai slodzei 2 kW, lai gan maksimālā slodze varētu pieaugt pat par 30 kW.

Mans plāns ir tāds, ka pirmās 10 līdz 15kW nodrošina saules bateriju paneļi, un divas 3kW (maksimālās) vējdzirnavas vējdzirnavas ir savvaļas maiņstrāvas, kas iztaisnotas līdz DC un 1000Ah 48 voltu akumulatoru bankai. (Ko es vēlētos novērst, lai iztukšotu / neizlādētos vairāk nekā 30% no tā jaudas, lai nodrošinātu akumulatora darbības laiku) mani ģeneratori apmierinātu atlikušo reto un ļoti periodisko enerģijas pieprasījumu.

Šī neregulārā un periodiskā slodze nāk no manas darbnīcas.

Esmu domājis, ka var būt saprātīgi izveidot kondensatora banku, lai apstrādātu vai uztvertu sistēmas atslābumu no visām induktīvās slodzes palaišanas strāvām, piemēram, motora uz mana gaisa kompresora un galda zāģa.

Bet šobrīd neesmu pārliecināts, vai nav labāka / lētāka veida.

Jūsu domas un komentāri būtu ļoti novērtēti un novērtēti. Es ceru, ka jums ir laiks atgriezties pie manis.

Jau iepriekš pateicos par veltīto laiku un uzmanību.

Ar cieņu Deivids nosūtīts no manas BlackBerry® bezvadu ierīces

Mana atbilde

Sveiks Deivid,

Esmu izlasījis jūsu prasību un, cerams, esmu to pareizi sapratis.

No 4 invertoriem tikai vienam būtu savs frekvences ģenerators, bet citiem darbotos, iegūstot frekvenci no šīs galvenās invertora izejas, un tādējādi visi būtu sinhronizēti savā starpā un ar šī galvenā invertora specifikācijām.

Es mēģināšu to noformēt un ceru, ka tas darbosies, kā paredzēts, un atbilstoši jūsu minētajām specifikācijām, tomēr ieviešana būs jāveic ekspertam, kuram jāspēj izprast koncepciju un pārveidot / pielāgot to līdz pilnībai, lai kur tas arī atrastos. nepieciešama .... citādi gūt panākumus ar šo samērā sarežģīto dizainu varētu kļūt ārkārtīgi grūti.

Es varu iepazīstināt tikai ar pamatkoncepciju un shēmu .... Pārējo vajadzēs veikt inženieriem no jūsu puses.

Man var paiet zināms laiks, līdz es to izpildu, jo man rindā jau ir daudz neapstiprinātu pieprasījumu ... Es jūs informēšu kā dēlu, kad tas ir izlikts

Ar cieņu Swag

2. e-pasts

Sveiks, Svagatam,

Liels paldies par ļoti ātru atbildi.

Tas nav gluži tas, ko es biju domājis, bet noteikti ir alternatīva.

Mana doma bija tāda, ka katrai ierīcei būs divas frekvences mērīšanas apakšshēmas, viena, kas aplūko frekvenci maiņstrāvas kopnes joslā, un šo vienību izmanto, lai izveidotu invertora sinusoidālo ģeneratoru pulksteņa impulsu.

Otra frekvences mērīšanas apakš ķēde aplūkotu invertora sinusoidālo ģeneratoru izvadi.

Būtu salīdzināšanas shēma, iespējams, izmantojot opamp masīvu, kas atgrieztos invertora sinusoidālā ģeneratora pulksteņa impulsā, lai virzītu pulksteņa signālu vai aizkavētu pulksteņa signālu, līdz sinusa viļņu ģeneratora izeja precīzi sakrīt ar sinhrono viļņu AC bar .

Kad invertora izejas posma frekvence sakritīs ar maiņstrāvas kopnes joslas frekvenci, būs SSR, kas slēgs invertora izejas posma savienošanu ar maiņstrāvas joslu, vēlams, nulles krustojuma punktā.

Tādā veidā kāds invertora modulis var izgāzties, un sistēma turpinās darboties. galvenā invertora mērķis bija tāds, ka no visiem invertora moduļiem tas nekad neiet gulēt un nodrošinās sākotnējo maiņstrāvas joslas frekvenci. tomēr, ja tas neizdodas, pārējās vienības tas netiks ietekmēts, kamēr viena ir “tiešsaistē”

Vergu vienībām jāatslēdzas vai jāiedarbojas, mainoties slodzei.

Jūsu novērojums bija pareizs. Es neesmu “elektronikas” vīrietis. Es esmu mehāniķis un elektroinženieris. Es strādāju ar lieliem augu priekšmetiem, piemēram, dzesētājiem, ģeneratoriem un kompresoriem.

Kad šis projekts virzās uz priekšu un sāk kļūt taustāmāks, vai jūs vēlētos / atvērtu pieņemt naudas dāvanu? Man nav daudz, bet es, iespējams, varētu pasniegt naudu caur paypal, lai palīdzētu atbalstīt jūsu vietnes mitināšanas izmaksas.

Paldies vēlreiz.

Ceru no jums dzirdēt.

namaste

Deivids

Mana atbilde

Paldies Deivid,

Būtībā jūs vēlaties, lai invertori būtu sinhronizēti savā starpā attiecībā uz frekvenci un fāzi, kā arī katram no tiem ir iespēja kļūt par galveno invertoru un pārņemt lādiņu, ja iepriekšējais kāda iemesla dēļ neizdodas. Pa labi?

Es mēģināšu to novērst ar jebkādām manām zināšanām un kādu veselo saprātu, nevis izmantojot sarežģītas IC vai konfigurācijas.

Sirsnīgākie sveicieni

3. e-pasts

Sveiks, Swag,

Tas viss ir riekstu čaumalā, ņemot vērā vienu papildu prasību.

Kad slodze samazinās, invertori pāriet uz eko vai gaidīšanas režīmu, un, palielinoties vai palielinoties slodzei, viņi pamostas, lai apmierinātu pieprasījumu.

Man patīk pieeja, ar kuru jūs ejat ...

Liels paldies, ka esat ļoti pateicīgs par mani.

Namaste

Ar cieņu

Deivids

Dizains

Pēc Dāvida kunga pieprasījuma ierosinātajām 4kva sakraujamajām barošanas invertoru ķēdēm jābūt 4 atsevišķu invertoru ķēdēm, kuras var atbilstoši sakraut sinhronizācijā ar otru, lai piegādātu pareizu pašregulējošās jaudas daudzumu savienotajam. slodzes, atkarībā no tā, kā šīs slodzes tiek ieslēgtas un izslēgtas.

ATJAUNINĀT:

Pēc dažām pārdomām es sapratu, ka dizainam patiesībā nav jābūt pārāk sarežģītam, drīzāk to varētu īstenot, izmantojot vienkāršu koncepciju, kā parādīts zemāk.

Nepieciešamajam invertoru skaitam būs jāatkārto tikai IC 4017 kopā ar saistītajām diodēm, tranzistoriem un transformatoru.

Oscilators būs viens gabals, un to var koplietot ar visiem invertoriem, integrējot tā pin3 ar IC 4017 pin14.

Atgriezeniskās saites ķēde ir precīzi jāpielāgo atsevišķiem invertoriem, lai nogriešanas diapazons būtu precīzi saskaņots ar visiem invertoriem.

Šos dizainus un paskaidrojumus var ignorēt, jo daudz vienkāršāka versija jau ir atjaunināta iepriekš

Invertoru sinhronizēšana

Galvenais izaicinājums šeit ir dot iespēju katram vergu invertoram būt sinhronizācijā ar galveno invertoru, kamēr galvenais invertors darbojas, un notikumā (kaut arī maz ticams) galvenais invertors neizdodas vai pārstāj darboties, nākamais invertors pārņem uzlādējas un pats kļūst par galveno invertoru.

Ja gadījumā arī otrais invertors neizdodas, trešais invertors uzņemas komandu un spēlē galvenā invertora lomu.

Patiesībā invertoru sinhronizēšana nav grūta. Mēs zinām, ka to var viegli izdarīt, izmantojot IC, piemēram, SG3525, TL494 utt. Tomēr sarežģītā dizaina daļa ir nodrošināt, ka, ja galvenais invertors neizdodas, viens no citiem invertoriem spēj ātri kļūt par galveno.

Un tas ir jāizpilda, nezaudējot kontroli pār frekvenci, fāzi un PWM pat uz sekundes daļu un ar vienmērīgu pāreju.

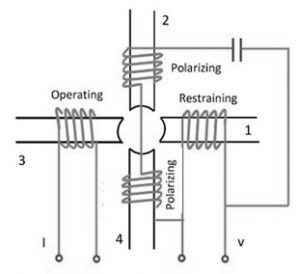

Es zinu, ka var būt daudz labāku ideju, un fundamentālākais dizains minēto kritēriju izpildei ir parādīts šajā diagrammā:

Iepriekš redzamajā attēlā mēs varam redzēt pāris identiskus posmus, kur augšējais invertors Nr. 1 veido galveno invertoru, bet apakšējais invertors - vergs.

Paredzams, ka uzstādīšanai jāpievieno vēl vairāki posmi invertora Nr. 3 un invertora Nr. 4 veidā, integrējot šos invertorus ar to atsevišķajiem optisko savienotāju posmiem, taču opamp posms nav jāatkārto.

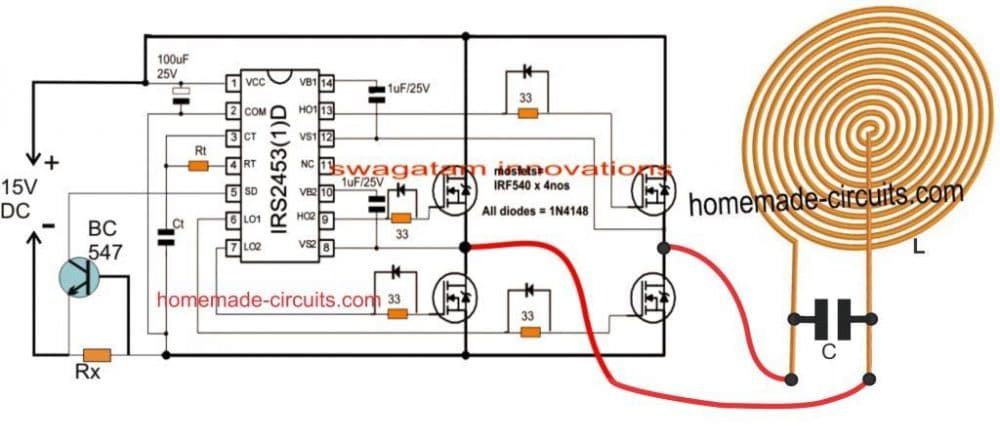

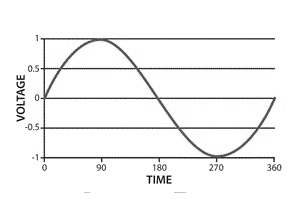

Dizains galvenokārt sastāv no IC 555 balstīta oscilatora un IC 4013 flip flop shēmas. IC 555 ir izveidots, lai ģenerētu pulksteņa frekvences ar ātrumu 100Hz vai 120Hz, kas tiek ievadīts IC 4013 pulksteņa ieejā, kas pēc tam pārveido to par nepieciešamo 50Hz vai 60Hz, pārmaiņus pārvēršot izejas ar augstu loģiku pāri tapai # 1 un tapu Nr. 2.

Pēc tam šīs mainīgās izejas tiek izmantotas barošanas ierīču aktivizēšanai un transformatoru paredzētās 220 V vai 120 V maiņstrāvas ģenerēšanai.

Kā jau iepriekš tika apspriests, izšķirošais jautājums šeit ir sinhronizēt divus invertorus tā, lai tie varētu darboties precīzi sinhronizēti attiecībā uz frekvenci, fāzi un PWM.

Sākotnēji visi iesaistītie moduļi (sakrautās invertora shēmas) tiek atsevišķi noregulēti ar precīzi identiskām sastāvdaļām, lai to uzvedība būtu pilnīgi līdzvērtīga vienam ar otru.

Tomēr pat ar precīzi saskaņotajiem atribūtiem nevar sagaidīt, ka invertori darbojas nevainojami sinhronizēti, ja vien tie nav saistīti kaut kādā unikālā veidā.

Tas faktiski tiek darīts, integrējot “vergu” invertorus caur opamp / optronu, kā norādīts iepriekš.

Sākotnēji galvenais invertors Nr. 1 ir ieslēgts, kas ļauj opamp 741 pakāpei darboties un inicializēt izejas sprieguma frekvenci un fāžu izsekošanu.

Kad tas ir uzsākts, visi nākamie invertori tiek ieslēgti, lai pievienotu strāvu elektrotīklam.

Kā redzams, opamp izeja ir savienota ar visu vergu invertoru laika kondensatoru caur opto savienotāju, kas piespiež vergu invertorus sekot galvenā invertora frekvencei un fāzes leņķim.

Tomēr interesanti šeit ir opamp fiksējošais faktors ar momentānās fāzes un frekvences informāciju.

Tas notiek, jo visi invertori tagad no galvenā invertora piegādā un darbojas noteiktā frekvencē un fāzē, kas nozīmē, ja gadījumā, ja kāds no invertoriem neizdodas, ieskaitot galveno invertoru, opamp spēj ātri izsekot un injicēt momentāno frekvenci / fāzes informācija un piespiest esošos invertorus darboties saskaņā ar šīm specifikācijām, un invertors savukārt spēj uzturēt atgriezenisko saiti uz opamp posmu, lai padarītu pārejas nevainojamas un pašoptimizējošas.

Tāpēc cerams, ka opamp posms rūpējas par pirmo izaicinājumu saglabāt visus piedāvātos sakraujamos invertorus perfekti sinhronizētus, izmantojot LIVE sekošanu pieejamai tīkla specifikācijai.

Raksta nākamajā daļā mēs uzzināsim sinhronizēta PWM sinewave pakāpe , kas ir nākamā izšķirošā iezīme iepriekš apspriestajā dizainā.

Šī raksta iepriekšminētajā daļā mēs uzzinājām 4kva sinhronizētā sakraujamā invertora ķēdes galveno sadaļu, kurā tika izskaidrotas dizaina sinhronizācijas detaļas. Šajā rakstā mēs pētām, kā padarīt dizainu par sinusa viļņu ekvivalentu, kā arī nodrošināt pareizu PWM sinhronizāciju starp iesaistītajiem invertoriem.

Sinhronā viļņa PWM sinhronizēšana starp invertoriem

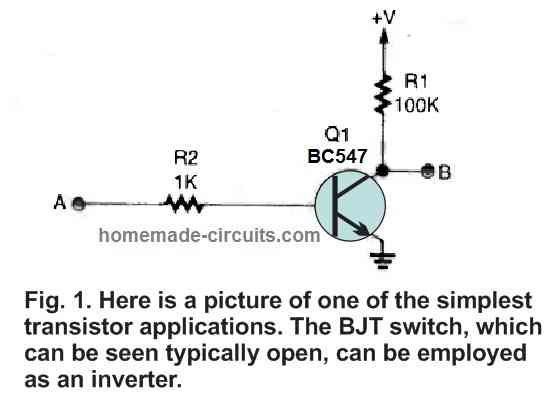

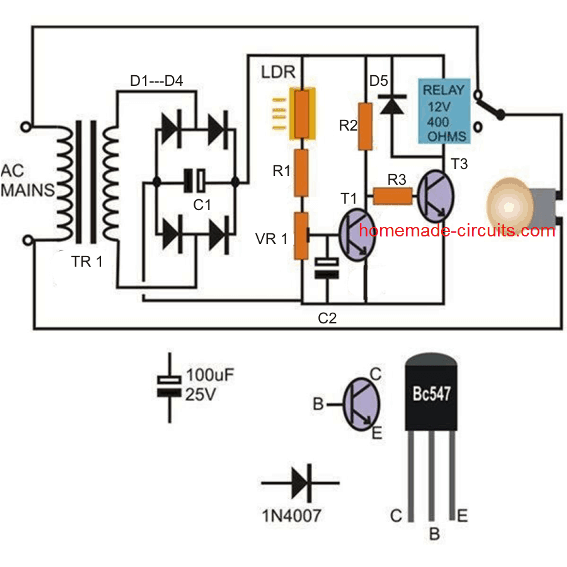

Vienkāršu RMS saskaņotu PWM ekvivalentu sinusviļņu viļņu formas ģeneratoru var izgatavot, izmantojot IC 555 un IC 4060, kā parādīts nākamajā attēlā.

Pēc tam šo konstrukciju var izmantot, lai invertori varētu izvadīt sinewave līdzvērtīgu viļņu formu pie to izejām un visā savienotajā tīkla līnijā.

Katrs no šiem PWM procesoriem būtu nepieciešams katram no sakraujamajiem invertora moduļiem atsevišķi.

ATJAUNINĀT: Šķiet, ka visu tranzistora bāzu sasmalcināšanai var izmantot vienu PWM procesoru, ja katra MJ3001 bāze savienojas ar konkrēto BC547 kolektoru, izmantojot atsevišķu 1N4148 diodi. Tas ļoti vienkāršo dizainu.

Dažādos posmos, kas saistīti ar iepriekš minēto PWM geneartoru ķēdi, var saprast, izmantojot šādu punktu:

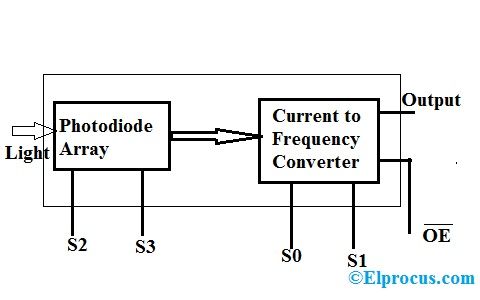

Izmantojot IC 555 kā PWM ģeneratoru

IC 555 ir konfigurēts kā PWM ģeneratora pamata ķēde. Lai vēlamajā RMS varētu ģenerēt regulējamus PWM ekvivalentos impulsus, IC ir vajadzīgi ātri trīsstūra viļņi pie tā tapas 7 un atskaites potenciāls pie pin5, kas nosaka PWM līmeni tā izejas tapā # 3

Izmantojot IC 4060 kā trīsstūra viļņu ģeneratoru

Trīsstūra viļņu ģenerēšanai IC 555 nepieciešami kvadrātveida viļņi pie tā tapas Nr. 2, kas iegūti no IC 4060 oscilatora mikroshēmas.

IC 4060 nosaka PWM biežumu vai vienkārši “pīlāru” skaitu katrā maiņstrāvas puscikla ciklā.

IC 4060 galvenokārt izmanto, lai pavairotu zemfrekvences parauga saturu no invertora izejas relatīvi augstā frekvencē no tā tapas Nr. 7. Paraugu biežums galvenokārt nodrošina, ka PWM sasmalcināšana ir vienāda un sinhronizēta visiem invertora moduļiem. Tas ir galvenais iemesls, kāpēc IC 4060 ir iekļauts, pretējā gadījumā citu IC 555 varēja viegli paveikt.

Atskaites potenciālu IC 555 tapā # 5 iegūst no opamp sprieguma sekotāja, kas parādīts ķēdes galējā kreisajā pusē.

Kā norāda nosaukums, šis opamp nodrošina tieši tādu pašu sprieguma lielumu pie tā tapas Nr. 6, kas parādās pie tā tapas Nr. 3 ... tomēr tās tapas Nr. 3 replikācija ar tapu Nr. 3 ir labi buferēta, un tāpēc tā ir bagātāka nekā tā pin3 kvalitāte, un tieši tāpēc šis posms ir iekļauts dizainā.

10 IC sākotnējais iestatījums, kas saistīts ar šī IC pin3, tiek izmantots RMS līmeņa pielāgošanai, kas galu galā precīzi noskaņo IC 555 izejas PWM līdz vēlamajam RMS līmenim.

Pēc tam šī RMS tiek piemērota barošanas ierīču bāzēm, lai piespiestu tās darboties norādītajos PWM RMS līmeņos, kas savukārt izeja AC iegūst pareizu RMS līmeni, iegūstot tīru sinusviļņu līdzīgu atribūtu. To var vēl vairāk uzlabot, izmantojot visu filtru izejas tinumā LC filtru.

Šīs 4kva sakraujamās sinhronizētās invertora ķēdes nākamajā un pēdējā daļā ir detalizēti aprakstīta automātiskās slodzes korekcijas funkcija, kas ļauj invertoriem piegādāt un uzturēt pareizo jaudas daudzumu izejas elektrotīkla līnijā atbilstoši mainīgajām slodžu pārslēgšanām.

Līdz šim mēs esam iekļāvuši divas galvenās prasības ierosinātajai sinhronizētajai 4kva sakraujošā invertora ķēdei, kas ietver frekvences, fāzes un PWM sinhronizāciju pāri invertoriem tā, ka neviena invertora kļūme iepriekšējos parametros neietekmēja pārējo .

Automātiska slodzes korekcijas stadija

Šajā rakstā mēs centīsimies noskaidrot automātiskās slodzes korekcijas funkciju, kas var ļaut invertorus secīgi ieslēgt vai izslēgt, reaģējot uz dažādiem slodzes apstākļiem visā izejas tīkla līnijā.

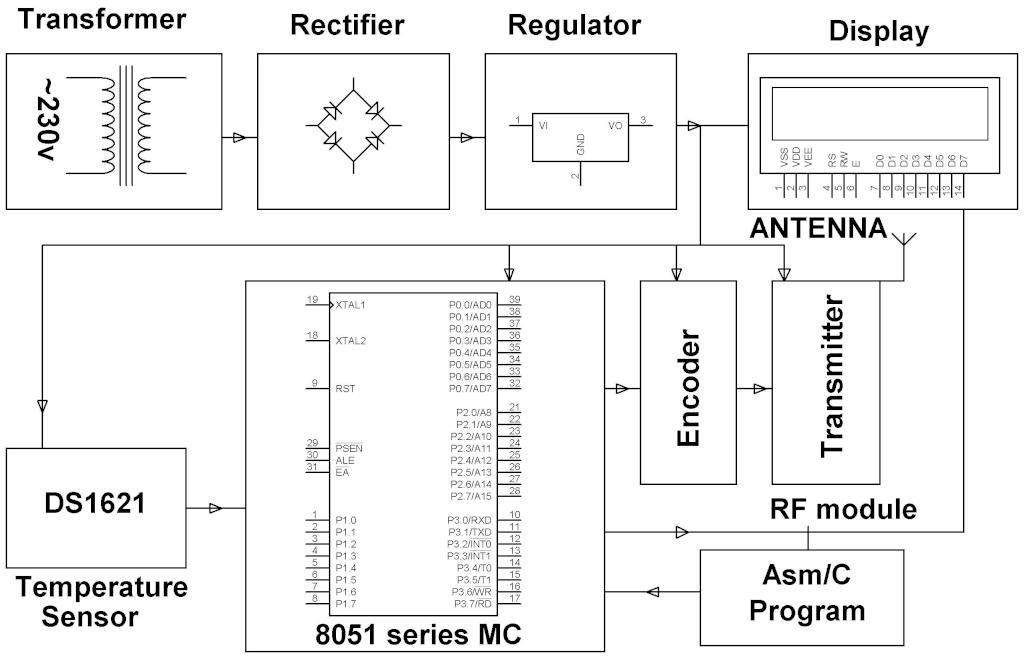

Lai ieviestu automātisku secīgas slodzes korekciju, kā norādīts šajā diagrammā, var izmantot vienkāršu kvadraciklu, izmantojot LM324 IC:

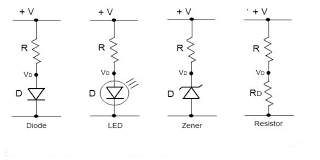

Iepriekš redzamajā attēlā mēs varam redzēt četrus IC LM324 opampus, kas konfigurēti kā četri atsevišķi salīdzinātāji ar to neinvertējošajām ieejām, kuras ir noregulētas ar atsevišķiem sākotnējiem iestatījumiem, savukārt uz visām to invertējošajām ieejām atsaucas ar fiksētu zenera spriegumu.

Attiecīgie sākotnējie iestatījumi tiek vienkārši noregulēti tā, lai opampi radītu augstas izejas secīgi, tiklīdz tīkla spriegums pārsniedz paredzēto slieksni ... un otrādi.

Kad tas notiek, attiecīgie tranzistori pārslēdzas atbilstoši opamp aktivizēšanai.

Attiecīgo BJT kolektori ir savienoti ar sprieguma sekotāja opamp IC 741 tapu # 3, kas tiek izmantots PWM kontroliera posmā, un tas liek opamp izejai kļūt zemai vai nullei, kas savukārt izraisa nulles sprieguma parādīšanos pie PWM IC 555 tapas # 5 (kā aprakstīts 2. daļā).

Izmantojot IC 555 tapu Nr. 5 ar šo nulles loģiku, piespiež PWM kļūt šaurāki vai ar minimālo vērtību, kā rezultātā šī konkrētā invertora izeja gandrīz izslēdzas.

Iepriekš minētās darbības mēģina stabilizēt izvadi agrākā normālā stāvoklī, kas atkal liek PWM kļūt plašākam, un šis virves vilkšana vai opampu pastāvīga pārslēgšana turpina konsekventi uzturēt izeju pēc iespējas stabilāku, reaģējot uz pievienoto slodžu variācijas.

Ar šo automātisko slodzes korekciju, kas ieviesta piedāvātajā 4kva sakraujošā invertora ķēdē, dizains gandrīz tiek pabeigts ar visām lietotāja pieprasītajām funkcijām raksta 1. daļā.

Pāri: Izveidojiet šo brīdinājumu SleepWalk - pasargājiet sevi no Sleepwalking Dangers Nākamais: IC 555 pinouts, Astable, Monostable, Bistable Shēmas ar izpētītajām formulām