Šajā rakstā mēs apspriedīsim daudzas dažādu ķēžu idejas, kas veidotas, izmantojot NAND vārtus no IC, piemēram, IC 7400, IC 7413, IC 4011 un IC 4093 utt.

IC 7400, IC 7413 specifikācijas

IC 7400 un 7413 ir 14 kontaktu DIL mikroshēmas vai '14 kontaktu divkāršās līnijas integrālās shēmas', kur 14. kontakts ir pozitīvais padeves V + un 7. kontakts ir negatīvais, iezemētais vai 0 V kontakts.

Barošanas avoti tapām 14 un 7 vienkāršības labad nav parādīti zīmējumos, taču ieteicams neaizmirst savienot šīs tapas, pretējā gadījumā ķēde vienkārši nedarbotos!

Visas ķēdes darbojas, izmantojot 4,5 V vai 6 V līdzstrāvas padevi, tomēr tipiskais spriegums var būt 5 volti. 5 V regulētu barošanu no tīkla var iegūt, izmantojot vairākas iespējas.

4 vārti no 7400 ir tieši tādi paši kā to specifikācijas:

- A vārtu tapas 1, 2 ieejas, 3. kontakta izeja

- B vārtu tapas 4, 5 ieejas, 6. kontakta izeja

- Vārtu C tapas 10, 9 ieejas, 8. kontakta izeja

- D vārtu kontakti 13, 12 ieejas, 11. kontakta izeja

Jūs varat atrast īpašu ķēdi, kas norāda oscilatoru, kas uzliek vārti A un B, taču tas arī nozīmē, ka to pašu var bez problēmām izveidot, izmantojot arī A un C, B un C vai C un D vārtus.

1. attēlā parādīta jūsu 7400 I.C. loģiskā shēma 2. attēlā parādīts loģiskais simboliskais attēlojums tikai vienam vārtiem, katram vārtiem parasti ir “2 ievades NAND vārti”.

Iekšējā konfigurācija ar atsevišķiem vārtiem ir parādīta 3. attēlā. 7400 ir TTL loģika I.C., tas nozīmē, ka tā darbojas, izmantojot 'Transistor-Transistor-Logic'. Katrā vārti izmanto četrus tranzistorus, katrs 7400 sastāv no 4 x 4 = 16 tranzistoriem.

Loģiskie vārti ietver stāvokļu pāri, atkarībā no binārās sistēmas, 1 vai 'Augsts', parasti 4 volti, un 0 (nulle) vai 'Zems', parasti 0 volti. Gadījumā, ja vārtu termināls netiek izmantots. kas var atbilst 1 ievadei.

Tas nozīmē, ka atvērto vārtu tapa ir 'augstā' līmenī. Kad vārtu ievades tapa ir savienota ar zemi vai 0 voltu līniju, tad ieeja kļūst 0 vai loģika zema.

NAND vārti faktiski ir 'NOT' un 'AND' vārtu sajaukums, ja abas tā ieejas (un funkcija) ir loģikā 1, izeja ir NOT vārtu izeja, kas ir 1.

NOT vārtu izeja būs 0 V, reaģējot uz 1 ieejas signālu vai + padeves ieeju, tas nozīmē, ka izeja būs loģiska nulle, kad ieeja ir + padeves līmenī.

NAND vārtiem, kad abas ieejas ir loģiskas 0, izeja pārvēršas par loģiku 1, kas ir tieši tāda pati kā vārtu NAV atbilde. Varētu šķist grūti saprast, kāpēc izeja ir 1, ja ieejas vērtība ir 0, un otrādi.

To var izskaidrot šādā veidā

Lai pārslēgtu stāvokli, jānotiek AND funkcijai, tas ir, katrai ieejai jāpārveidojas stāvokļa pārslēgšanai.

Tas notiek tikai tad, kad abas ieejas pārslēdzas no 0 uz 1. 7400 vārti ir 2 ieejas NAND vārti, tomēr 3 ievades NAND vārti 7410 IC, 4 ieejas NAND vārti 7420 un arī 8 ieejas NAND vārti 7430 var tikt viegli iegādāti arī no tirgus. .

Attiecībā uz 7430 tā 8 ieejas vārti pārslēdzas stāvoklī tikai tad, kad katra no 8 ieejām ir 1 vai 0.

Kad 7430 8 ieejas ir 1,1,1,1,1,1,1,0, tad izeja joprojām būs 1. Stāvokļa maiņa nenotiks, kamēr visām 8 ieejām nebūs identiskas loģikas .

Bet tiklīdz pēdējā ievade mainās no 0 uz 1, izeja mainās no 1 uz 0. Tehnika, kas izraisa “stāvokļa maiņu”, ir izšķirošs aspekts, lai izprastu loģisko ķēžu funkcionalitāti.

Piespraudes, kurām parasti var būt loģiskā IC, ir 14 vai 16. 7400 sastāv no četriem NAND vārtiem, ar 2 ieejas tapām un 1 izejas tapu katram no vārtiem, kā arī pāris tapu barošanas avota ieejām, tapai 14 un 7. tapa.

IC 7400 ģimene

Pārējiem 7400 ģimenes locekļiem var būt lielāks ieejas tapu skaits, piemēram, 3 ieejas NAND vārti, 4 ieejas NAND vārti un 8 ieejas NAND vārti ar vairākām ieejas kombinācijas opcijām katram vārtiem. Kā piemēru IC 7410 ir 3 ieejas NAND vārtu vai “Triple 3 ievades NAND vārtu” variants.

IC 7420 ir 4 ieejas NAND vārtu variants, un to sauc arī par “Dual 4 input NAND gate”, savukārt IC 7430 ir loceklis, kuram ir 8 ieejas, un to sauc par 8 ieejas NAND vārtiem.

NAND vārtu pamata savienojumi

Lai arī IC 7400 ir tikai NAND vārti, NAND vārtus iespējams savienot vairākos veidos.

Tas ļauj mums tos pārveidot citos vārtu veidos, piemēram:

(1) invertora vai vārti “NAV”

(2) AND vārti

(3) VAI vārti

(4) NOR vārti.

IC 7402 atgādina 7400, lai gan to veido 4 NOR vārti. Tāpat kā NAND ir kombinācija “NOT plus AND”, NOR ir maisījums “NOT plus OR”.

7400 ir ārkārtīgi pielāgojams IC, ko var atrast no ķēžu diapazona sekošanas lietojumprogrammu ceļvedī.

Lai palīdzētu jums pilnībā izprast NAND vārtu funkcionalitāti, iepriekš ir parādīta PATIESĪBU tabula 2 ievades NAND vārtiem.

Līdzvērtīgas patiesības tabulas varētu novērtēt gandrīz visiem loģikas vārtiem. Patiesības tabula 8 ievades vārtiem, piemēram, 7430, ir nedaudz sarežģītāka.

Kā pārbaudīt NAND Gate

Lai pārbaudītu 7400 IC, jūs varat darbināt strāvu starp tapām 14 un 7. Turiet 1. un 2. tapas savienotas ar pozitīvo padevi, tas parādīs izvadi kā 0.

Pēc tam, nemainot 2. kontakta savienojumu, pievienojiet 1. kontaktu 0 voltiem. Tas ļaus ieejām kļūt par 1, 0. Tādējādi izeja pagriezīsies par 1, izgaismojot LED. Tagad vienkārši nomainiet 1. un 2. kontaktu savienojumus, lai ieejas kļūtu par 0, 1, tas izeju pārslēgs uz loģiku 1, izslēdzot LED.

Pēdējā solī pievienojiet gan ieejas tapas 1, gan 2 uz zemi vai 0 voltiem, lai ieejas būtu 0, 0. Loģika atkal ieslēdz izejas loģiku augstu vai 1, ieslēdzot LED. LED spīdēšana nozīmē 1. loģikas līmeni.

Kad LED ir izslēgts, tas norāda uz loģisko līmeni 0. Analīzi varētu atkārtot vārtiem B, C un D.

Piezīme: katra no šeit pārbaudītajām ķēdēm darbojas ar 1 / 4W 5% rezistoriem - visiem elektrolītiskajiem kondensatoriem parasti ir 25V nomināls.

Ja ķēde nedarbojas, varat apskatīt savienojumus, kļūdainas IC iespējamība var būt ļoti maz ticama, salīdzinot ar nepareizu tapu savienojumu. Šie zemāk redzamo NAND vārtu savienojumi var būt visvienkāršākie un darbojas, izmantojot tikai 1 7400 vārtu.

1) NAV vārti no NAND vārtiem

Kad NAND vārtu ieejas tapas a ir īssavienotas, ķēde darbojas kā invertors, tas nozīmē, ka izejas loģika vienmēr parāda pretējo ieejai.

Kad vārtu saīsinātās ieejas tapas ir savienotas ar 0V, izeja pārvēršas par 1 un otrādi. Tā kā “NOT” konfigurācija nodrošina pretēju reakciju visā ieejas un izejas tapās, tāpēc nosaukums NOT gate. Šī frāze faktiski ir tehniski piemērota.

2) Vārtu izveidošana no NAND vārtiem

Tā kā NAND vārti ir arī sava veida vārdi “NOT UN”, tādēļ gadījumā, ja pēc NAND vārtiem tiek ieviesti vārti “NOT”, ķēde pārvēršas par “NOT NOT AND” vārtiem.

Pāris negatīvs rada pozitīvu (jēdziens, kas ir populārs arī matemātikas jēdzienos). Ķēde tagad ir kļuvusi par “AND” vārtiem, kā parādīts iepriekš.

3) VAI vārtu izgatavošana no NAND vārtiem

Ievietojot NOT vārtus pirms katras NAND vārtu ieejas, tiek ģenerēti vārti VAI, kā parādīts iepriekš. Parasti tie ir 2 ievades VAI vārti.

4) NOR vārtu izgatavošana no NAND vārtiem

Iepriekšējā dizainā mēs izveidojām OR vārti no NAND vārtiem. NOR vārti faktiski kļūst par NOT VAI vārtiem, kad mēs pievienojam papildu NOT vārtus tieši aiz OR vārtiem, kā parādīts iepriekš.

5) Loģikas līmeņa testeris

Šo loģikas līmeņa pārbaudīto ķēdi var izveidot, izmantojot vienus 7400 NAND vārtus kā invertoru vai NAV vārtus loģisko līmeņu norādīšanai. Pāris sarkanas gaismas diodes tiek izmantotas, lai atšķirtu loģikas līmeņus starp LED 1 un LED 2.

Garākā LED tapa kļūst par katoda vai LED negatīvo tapu. Kad ievade ir 1. loģikas līmenī vai HIGH, 1. gaismas diode iedegas dabiski.

Adata 3, kas ir izejas tapa, ir pretēja ieejai pie loģikas 0, kā rezultātā gaismas diode 2 paliek izslēgta. Kad ievade saņem loģiku 0, gaismas diode 1 dabiski izslēdzas, bet gaismas diode 2 tagad spīd pretējas vārtu reakcijas dēļ.

6) BISTABILA FĒLE (S.R. FLIP-FLOP)

Šajā shēmā tiek izmantoti pāris NAND vārti, kas ir savstarpēji savienoti, lai izveidotu S-R bistable fiksatora ķēdi.

Izejas ir apzīmētas kā Q un 0. Līnija virs Q apzīmē NOT. 2 izejas Q un 0 darbojas kā viens otra papildinājumi. Nozīme, kad Q sasniedz 1. loģikas līmeni, Q pagriežas 0, kad Q ir 0, Q pagriežas 1.

Kontūru varēja aktivizēt abos 2 stabilajos stāvokļos, izmantojot atbilstošu ieejas impulsu. Būtībā tas ļauj ķēdei izmantot “atmiņas” funkciju un izveido to ļoti vienkāršā 1 bitu (viena binārā cipara) datu glabāšanas mikroshēmā.

Abas ieejas ir apzīmētas ar S un R vai Iestatīt un Atiestatīt, tāpēc šo ķēdi parasti sauc par S.R.F.F. ( Iestatiet Atiestatīt Flip-Flop ). Šī shēma var būt diezgan noderīga, un to izmanto vairākās ķēdēs.

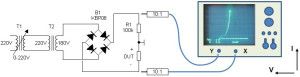

S-R FLIP-FLOP taisnstūrveida viļņu ģenerators

SR Flip-Flop shēmu var konfigurēt tā, lai tā darbotos kā kvadrātveida viļņu ģenerators. Ja F.F. tiek izmantots ar sinusa viļņu, pieņemsim, ka no transformatora 12 V maiņstrāvas ar minimālo 2 voltu maksimumu līdz maksimuma diapazonu, izeja reaģēs, ģenerējot kvadrātveida viļņus, kuru maksimums līdz maksimums ir ekvivalents Vcc spriegumam.

Var sagaidīt, ka šie kvadrātveida viļņi būs pilnīgi kvadrātveida formas, pateicoties ļoti straujai IC pieauguma un krituma laikam. Invertora vai NOT vārtu izeja, kas baro R ieeju, rada papildu ON / OFF ieejas visā ķēdes R un S ieejās.

8) IESLĒGT KONTAKTU SASTĀVDAĻU ELIMINATORU

Šajā ķēdē S-R FLIP-FLOP var uzskatīt par piemērotu kā slēdža kontakta atlēcienu.

Ikreiz, kad slēdža kontakti ir aizvērti, tam parasti seko kontakti, kas mehāniskās sprieguma un spiediena dēļ pāris reizes strauji atlec.

Tas galvenokārt rada viltus tapas, kas var izraisīt traucējumus un nepareizu ķēdes darbību.

Iepriekš minētā shēma izslēdz šo iespēju. Kad kontakti sākotnēji aizveras, tas tiek fiksēts ķēdē, un tādēļ kontakta atlēciena iejaukšanās nerada nekādu efektu uz flip-flop.

9) ROKAS Pulkstenis

Tas ir vēl viens astotās ķēdes variants. Lai eksperimentētu ar ķēdēm, piemēram, pusapvienotāju vai citām loģiskām ķēdēm, patiešām ir jāspēj analizēt ķēde, jo tā vienlaikus darbojas ar vienu impulsu. To varēja panākt, izmantojot rokas vadību.

Ikreiz, kad slēdzis tiek pārslēgts, pie izejas parādās vientuļš sprūda. Ķēde darbojas ārkārtīgi labi ar bināro skaitītāju. Ikreiz, kad slēdzis tiek pārslēgts, ķēdes pret atlēciena iezīmes dēļ vienlaikus var notikt tikai viens impulss, kas ļauj skaitīšanai progresēt vienu sprūdu vienlaikus.

10) S-R FLIP-FLOP AR ATMIŅU

Šī shēma ir veidota, izmantojot pamata S-R Flip-Flop. Rezultātu nosaka pēdējā ievade. D norāda DATA ievadi.

Vārtu B un C aktivizēšanai ir nepieciešams impulss “iespējot”. Q veido tādu pašu loģisko līmeni kā D, tas nozīmē, ka tas pieņem D vērtību un joprojām atrodas šajā stāvoklī (sk. 14. attēlu).

Piespraudes numuri nav norādīti vienkāršības labad. Visi 5 vārti ir 2 ieejas NAND, nepieciešami pāris 7400. Iepriekš redzamā diagramma apzīmē tikai loģisko shēmu, taču to var ātri pārveidot par shēmas shēmu.

Tas racionalizē diagrammas, kurās ir milzīgs daudzums loģiskie vārti darbam ar. Iespējas signāls varētu būt impulss no iepriekš paskaidrotās “manuālās pulksteņa ķēdes”.

Ķēde darbojas ikreiz, kad tiek izmantots “CLOCK” signāls, tas parasti ir pamatprincips, kas tiek izmantots visās ar datoru saistītajās lietojumprogrammās. Pāris iepriekš paskaidrotās shēmas var izveidot, izmantojot tikai divus 7400 IC, kas ir savienoti viens ar otru.

11) Pulksteņa kontrolēta flip-flop

Tas faktiski ir cita veida SR flip flop ar atmiņu. Datu ievadi regulē pulksteņa signāls, izvadi caur S-R Flip-Flop tāpat regulē pulkstenis.

Šis Flip-Flop darbojas labi kā glabāšanas reģistrs. Pulkstenis faktiski ir impulsu ievades un izvades kustības galvenais kontrolieris.

12) AUGSTĀ ātruma impulsa indikators un detektors

Šī konkrētā shēma ir veidota, izmantojot S-R Flip -Flop, un ir pieradusi uztvert un parādīt noteiktu impulsu loģiskajā ķēdē.

Šis impulss fiksē ķēdi, pēc tam izeja tiek lietota invertora ieejai, kas izraisa sarkanās gaismas diode spīdēšanu.

Ķēde joprojām atrodas šajā konkrētajā stāvoklī, līdz tā tiek novērsta, pārslēdzot viena pola slēdzis, atiestatīšanas slēdzis .

13) 'SNAP!' RĀDĪTĀJS

Šī shēma parāda, kā S-R Flip-Flop izmantot citā veidā. Lūk, divi flip-flops ir iestrādāti caur 7 NAND vārtiem.

Fundamentālā teorija šajā ķēdē ir S-R flip-flops un INHIBIT līniju izmantošana. SI un S2 veido slēdžus, kas vada flip-flops.

Brīdī, kad flip fiksē attiecīgo LED, ieslēdzas un tiek novērsta papildu flip-flop fiksācija. Kad slēdži ir spiedpogu formā, pogas atlaišana izraisa ķēdes atiestatīšanu. Izmantotās diodes ir 0A91 vai jebkurš cits, piemēram, 1N4148.

- Vārti A, B, C veido skatuvi S1 un LED 1.

- Vārti D, E, F veido posmu S2 un LED 2.

- Vārti G apstiprina, ka INHIBIT un INHIBIT līnijas darbojas kā papildinoši pāri.

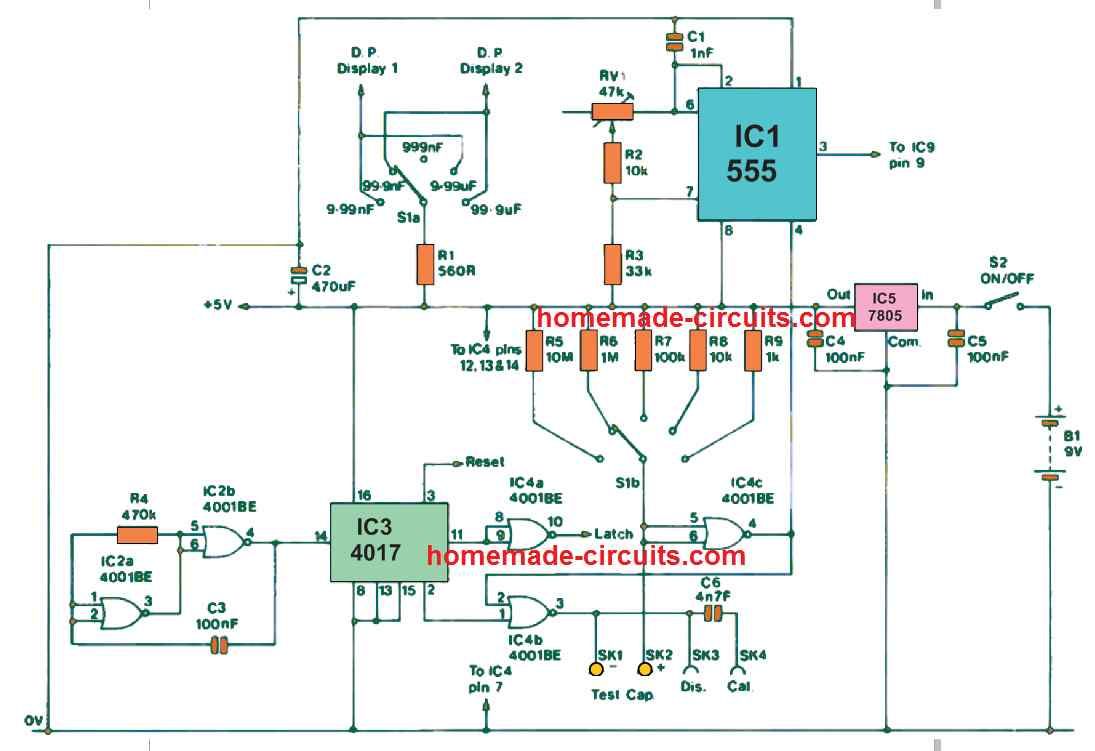

14) ZEMAS FREKVENCES AUDIO OSCILATORS

Kontūrā tiek izmantoti divi NAND vārti, kas savienoti kā invertori un ir savstarpēji savienoti, lai izveidotu astabilu multivibratoru.

Biežumu var mainīt, palielinot CI un C2 vērtību (zemāka frekvence) vai samazinot C1 un C2 vērtību (augstāka frekvence). Kā elektrolītiskie kondensatori pārliecinieties, vai polaritātes savienojums ir pareizs.

Piecpadsmit, sešpadsmit un septiņpadsmit ķēdes ir arī zemas frekvences oscilatoru veidi, kas izveidoti no četrpadsmit ķēdes. Tomēr šajās ķēdēs izeja ir konfigurēta tā, lai gaismas diodes mirgot.

Mēs varam novērot, ka visas šīs ķēdes ir diezgan līdzīgas viena otrai. Tomēr šajā ķēdē, ja pie izejas tiek izmantots gaismas diode, gaismas diode mirgo ļoti ātri, ko mūsu acis praktiski nevar atšķirt redzes noturības dēļ. Šis princips tiek izmantots kabatas kalkulatori .

15) TWIN LED Zibspuldze

Šeit mēs iekļaujam pāris NAND vārtus, lai izveidotu ļoti zemas frekvences oscilatoru. The dizains kontrolē divas sarkanās gaismas diodes izraisot gaismas diodes mirgošanu ar alternatīvu ON OFF pārslēgšanu.

Ķēde darbojas ar diviem NAND vārtiem, pārējos divus IC vārtus varētu papildus izmantot tajā pašā ķēdē. Šai otrajai shēmai varētu izmantot dažādas kondensatora vērtības, lai ģenerētu alternatīvu LED mirgojošo posmu. Lielākas vērtības kondensatori izraisīs gaismas diodes lēnāku mirgošanu un otrādi.

16) VIENKĀRŠA LED STROBOSKOPS

Šis īpašais dizains tiek ražots no piecpadsmitās ķēdes, kas darbojas kā mazjaudas stroboskops. Ķēde faktiski ir liels ātrums LED spuldze . Sarkanā gaismas diode ātri raustās, bet acs cenšas atšķirt specifiskos zibšņus (redzes noturības dēļ).

Nevar gaidīt, ka izejas gaisma būs pārāk spēcīga, kas nozīmē, ka stroboskops var darboties labāk tikai tad, kad ir tumšs, nevis dienas laikā.

Grupētie mainīgie rezistori tiek izmantoti, lai mainītu stroba frekvenci tā, lai stroboskops var viegli pielāgot jebkuram vēlamajam strobe ātrumam.

Stroboskops darbojas ārkārtīgi labi augstākās frekvencēs, mainot laika kondensatora vērtību. Gaismas diode, kas faktiski ir diode, spēj viegli atbalstīt ļoti augstas frekvences. Mēs iesakām to izmantot, lai šajā ķēdē uzņemtu ļoti ātrus attēlus.

17) ZEMAS HISTĒZES ŠMITTA TRIGERIS

Divas NAND vārtu funkcijas var būt konfigurētas kā a Šmita sprūda lai izveidotu šo konkrēto dizainu. Lai eksperimentētu ar šo ķēdi, varat pielāgot R1, kas ir novietots histerēzes efekts .

18) PAMATFREKVENCES KRISTĀLA OSCILATORS

Šī shēma tiek izmantota kā kristāla vadīts oscilators. Vārtu pāri tiek vadīti kā invertori, rezistori nodrošina pareizu saistīto vārtu izspiešanas apjomu. 3. vārti ir konfigurēti kā “buferis”, kas novērš oscilatora pakāpes pārslodzi.

Atcerieties, ka tad, kad šajā konkrētajā ķēdē tiek izmantots kristāls, tas svārstīsies savā pamatfrekvencē, proti, tas netiks svārstīts harmoniskajā vai pieskaņotajā frekvencē.

Gadījumā, ja ķēde darbojas ar ievērojami samazinātu frekvenci, nekā tika lēsts, tas nozīmētu, ka kristāla frekvence darbojas ar pieskaņu. Citiem vārdiem sakot, tas var darboties ar vairākām pamata frekvencēm.

19) DIVBITU DEKODĒTĀJS

Šī shēma ir vienkāršs divu bitu dekoders. Ieejas ir pāri līnijai A un B, izejas - pāri līnijai 0, 1, 2, 3.

Ieeja A var būt kā loģika 0 vai 1. Ieeja B var būt kā loģika 0 vai 1. Ja A un B abi tiek lietoti ar loģiku 1, tas kļūst par bināro skaitli 11, kas ir vienāds ar denāriju 3 un izvadi pāri līnijai 3 ir 'augsts'.

Tāpat arī A, 0 B, 0 izejas rinda 0. Vislielākais skaitlis ir balstīts uz izejvielu daudzumu. Lielākais skaitītājs, izmantojot 2 ieejas, ir 22 - 1 = 3. Var būt iespējams pagarināt ķēdi vēl vairāk, piemēram, ja tika izmantotas četras ieejas A, B, C un D, tādā gadījumā lielākais skaitlis būs 24 - 1 = 15 un izejas ir no 0 līdz 15.

20) FOTOJŪTĪGA NOSLĒGUMA APRĪKOJUMS

Tas ir vienkārši fotodetektora shēma kas izmanto pāris NAND vārtus, lai aktivizētu tumsā aktivizētu fiksācijas darbību.

Kad apkārtējā gaisma ir augstāka par iestatīto slieksni, izeja paliek neietekmēta un loģiski nulles. Kad tumsa nokrītas zem noteiktā sliekšņa, NAND vārtu ieejas potenciāls pārslēdz to uz augstu loģiku, kas savukārt izvadi pastāvīgi fiksē augstā loģikā.

Diodes noņemšana noņem fiksācijas funkciju, un tagad vārti darbojas vienlaikus ar gaismas reakcijām. Tas nozīmē, ka, reaģējot uz fotodetektora gaismas intensitāti, izeja pārmaiņus ir augsta un zema.

21) DVĪŅU TONU AUDIO OSCILATORS

Nākamais dizains parāda, kā izveidot a divu toņu oscilators izmantojot divus NAND vārtu pārus. Izmantojot šos NAND vārtus, tiek konfigurēti divi oscilatoru posmi, no kuriem vienam ir augsta frekvence, izmantojot 0,22 µF, bet otram ar zemas frekvences oscilatoru 0,47 uF kondensatoriem.

Oscilatori savienoti viens ar otru tādā veidā, ka zemfrekvences oscilators modulē augstfrekvences oscilatoru. Tas rada a rīboša skaņas izeja kas izklausās patīkamāk un interesantāk nekā mono tonis, ko rada 2 vārtu oscilators.

22) KRISTĀLA Pulksteņa OSCILATORS

Tas ir cits kristāla bāzes oscilatora ķēde lietošanai ar L.S.I. IC pulksteņa 'mikroshēma' 50 Hz bāzei. Izvade tiek noregulēta 500 kHz frekvencē, tāpēc, lai iegūtu 50 Hz, šī izeja ir jāpievieno četrām 7490 I.C. kaskādes veidā. Katrs 7490 pēc tam sadala nākamo produkciju ar 10, ļaujot kopējo sadalījumu 10 000.

Tas beidzot rada izeju, kas vienāda ar 50 Hz (500 000 10 ÷ 10 ÷ 10+ 10 = 50). 50 Hz atskaite parasti tiek iegūta no elektrotīkla, taču, izmantojot šo ķēdi, pulkstenis var būt neatkarīgs no elektrotīkla, kā arī iegūt tikpat precīzu 50 Hz laika bāzi.

23) IESLĒGTS OSCILATORS

Šī shēma sastāv no toņu ģeneratora un komutācijas pakāpes. Toņu ģenerators darbojas bez apstājas, bet bez jebkādas izejas uz klausules.

Tomēr, tiklīdz pie ieejas vārtiem A parādās loģika 0, tā vārtu A pārveido par loģiku 1. Loģika 1 atver vārtus B, un skaņas frekvencei ir atļauts sasniegt klausuli.

Kaut arī šeit tiek izmantots niecīgs kristāla auss, tas joprojām spēj radīt pārsteidzoši skaļu skaņu. Kontūru, iespējams, varētu izmantot kā skaņas signālu, kura malā ir elektroniskais modinātājs I.C.

24) KĻŪDU SPrieguma detektors

Šī shēma ir paredzēta darbam kā fāzes detektors caur četriem NAND vārtiem. Fāzes detektors analizē divas ieejas un rada kļūdas spriegumu, kas ir proporcionāls starpībai starp abām ieejas frekvencēm.

Detektora izeja pārveido signālu caur RC tīklu, kas sastāv no 4k7 rezistora un 0,47uF kondensatora, lai radītu līdzstrāvas kļūdas spriegumu. Fāzes detektora shēma darbojas ārkārtīgi labi P.L.L. (fāzes bloķēšanas cilpa) lietojumprogrammas.

Iepriekš redzamajā diagrammā parādīta pilnas P.L.L. tīklā. Fāzes detektora radītais kļūdas spriegums tiek palielināts, lai regulētu multivibratora frekvenci V.C.O. (ar spriegumu kontrolēts oscilators).

P.L.L. ir neticami noderīgs paņēmiens un ir ļoti efektīvs F.M demodulācijā ar 10,7 MHz (radio) vai 6 MHz (TV skaņa) vai atjaunojot 38 KHz apakšnesēju stereo multipleksā dekoderī.

25) RF vājinātājs

Dizainā ir iekļauti 4 NAND vārti un tie tiek piemēroti smalcinātāja režīmā, lai kontrolētu diode tiltu.

Diodes tilta slēdži vai nu ļauj vadīt RF, vai arī bloķēt RF.

Cik daudz RF ir atļauts caur kanālu, galu galā nosaka vārtu signāls. Diodes var būt jebkuras ātrgaitas silīcija diodes vai pat mūsu pašu 1N4148 darbosies (skat. 32. diagrammu).

26) ATSAUCES BIEZUMA Slēdzis

Ķēde darbojas ar pieciem NAND vārtiem, lai izstrādātu 2 frekvences slēdzi. Šeit, lai neitralizētu SPDT slēdža atstarošanas efektu, tiek izmantota bistabila aizbīdņa ķēde kopā ar viena pola slēdzi. Galīgā izeja var būt f1 vai f2, atkarībā no SPDT pozīcijas.

27) Divu bitu datu pārbaude

Šī shēma darbojas ar datora tipa koncepciju, un to var izmantot, lai apgūtu loģikas pamatfunkcijas, kas rodas datorā, kā rezultātā rodas kļūdas.

Kļūdu pārbaude tiek veikta, pievienojot papildu bitu (bināro ciparu) vārdos, lai galīgā summa, kas parādās datora vārdā, būtu vienmēr nepāra vai pāra.

Šo metodi sauc par “PARITĀTES PĀRBAUDI”. Shēma pārbauda nepāra vai pāra paritāti 2 bitiem. Mēs varam konstatēt, ka dizains diezgan atgādina fāzes kļūdu detektora shēmu.

28) BINĀRĀ PUSES PAPILDINĀTĀJU APRITE

Šajā shēmā tiek izmantoti septiņi NAND vārti, lai izveidotu a puse papildinātāja ķēde . A0, B0 veido bināro ciparu ieejas. S0, C0 apzīmē summu un nesošās līnijas. Lai varētu uzzināt, kā darbojas šāda veida shēmas, iedomājieties, kā matemātika tiek izglītota bērniem. Jūs varat atsaukties uz zemāk redzamo tabulu ar pusapkopojuma PATIESĪBU.

- 0 un 0 ir 0

- Es un 0 ir summa 1, kas ir 0.

- 0 un 1 ir summa 1, kas nes 0.

- Es un es ir 10 summa 0 pārvadāt 1.

1 0 nevajadzētu kļūdīties kā “desmit”, drīzāk to izrunā kā “vienu nulli” un tas simbolizē 1 x 2 ^ 1 + (0 x 2 ^ 0). Divas veselas puspapildu ķēdes papildus “OR” vārtiem rada pilnu papildinātāju ķēdi.

Šajā diagrammā A1 un B1 ir binārie cipari, C0 ir pārnesums no iepriekšējā posma, S1 kļūst par summu, C1 ir pārnese uz nākamo posmu.

29) NOR VĀRTU PUSES PAPILDINĀTĀJS

Šī ķēde un nākamās zemāk ir konfigurētas, izmantojot tikai NOR vārtus. 7402 IC nāk ar četriem 2 ieejas NOR vārtiem.

Puse papildinātājs darbojas ar piecu NOR vārtu palīdzību, kā parādīts iepriekš.

Izejas līnijas:

30) NOR VĀRTU PILNA PAPILDINĀTĀJS

Šis dizains attēlo pilnu papildinātāju ķēdi, izmantojot pāris NOR vārtu puspapildinātājus kopā ar pāris papildu NOR vārtiem. Ķēde darbojas kopā ar 12 NOR vārtiem un vajadzībām visos 340 no 7402 I.C.s. Izejas līnijas ir:

Ievades līnijas A, B un K.

K faktiski ir cipars, kas virzās uz priekšu no iepriekšējās rindas. Ievērojiet, ka izeja tiek realizēta ar pāris NOR vārtiem, kas ir vienādi ar vieniem VAI vārtiem. Ķēde noslēdzas ar diviem puspapildinātājiem papildus OR vārtiem. Mēs to varam salīdzināt ar mūsu iepriekš apspriestajām shēmām.

31) VIENKĀRŠS SIGNĀLA INJEKTORS

Pamata signāla inžektors ko var izmantot audioiekārtu defektu vai citu ar frekvenci saistītu problēmu pārbaudei, varētu izveidot, izmantojot divus NAND vārtus. Ierīce sērijveidā izmanto 4,5 V spriegumu caur 3nos 1,5 V AAA elementu (sk. 42. diagrammu).

Vēl vienu signāla inžektora shēmu var uzbūvēt, kā parādīts zemāk, izmantojot pusi 7413 IC. Tas ir ticamāk, jo tas izmanto Schmitt trigeri kā multivibratoru

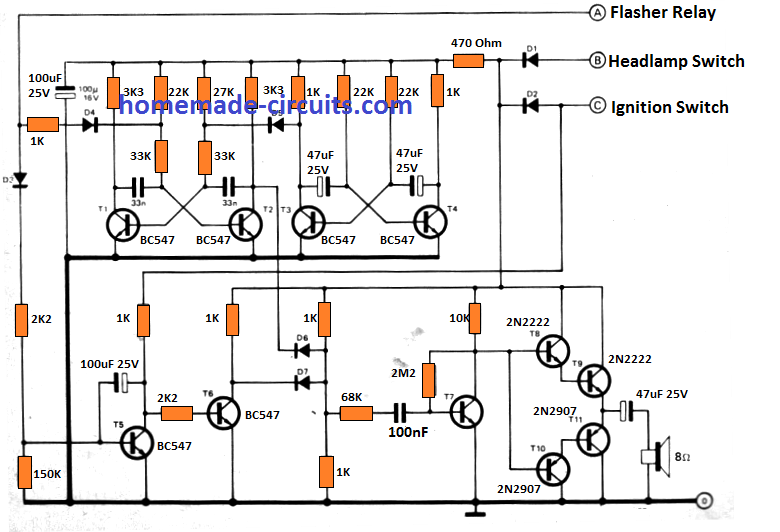

32) VIENKĀRŠS PASTIPRINĀTĀJS

Pāris NAND vārtu, kas paredzēti kā invertori, varētu būt virknē vadi, lai izstrādātu a vienkāršs audio pastiprinātājs . 4k7 rezistors tiek izmantots, lai radītu negatīvu atgriezenisko saiti ķēdē, lai gan tas nepalīdz novērst visus traucējumus.

Pastiprinātāja izeju var izmantot ar jebkuru skaļruni, kura nominālā vērtība ir no 25 līdz 80 omiem. Var izmēģināt 8 Ohm skaļruni, lai gan tas varētu izraisīt daudz siltāku IC.

Varētu izmēģināt arī zemākas 4k7 vērtības, bet tas var novest pie zemākas izejas skaļuma.

33) Zema ātruma pulkstenis

Šeit Schmitt trigeris tiek izmantots kopā ar zemas frekvences oscilatoru, RC vērtības nosaka ķēdes frekvenci. Pulksteņa frekvence ir aptuveni 1 Hz vai 1 impulss sekundē.

34) NAND vārtu skārienekrāna ķēde

Tikai pāris NAND var izmantot a ar skārienu darbināms relejs vadības slēdzis, kā parādīts iepriekš. Pamata konfigurācija ir tāda pati kā iepriekš paskaidrotais RS flip flip, kas iedarbina tā izvadi, reaģējot uz diviem skārienpaliktņiem to ieejās. Pieskaroties skārienpaliktnim 1, izeja palielinās, aktivizējot releja draivera pakāpi, tā ka pievienotā slodze tiek ieslēgta.

Kad pieskaras apakšējam skārienpaliktnim, tā izejvielu atiestata, pagriežot to atpakaļ uz loģisko nulli. Šī darbība izslēdz stafetes vadītājs un slodze.

35) PWM vadība, izmantojot vienus NAND Gate

NAND vārtus var izmantot arī efektīvas PWM kontrolētas izejas sasniegšanai no minimālā līdz maksimālajam.

Kreisajā pusē redzamie NAND vārti veic divas lietas, tas rada nepieciešamo frekvenci, kā arī ļauj lietotājam atsevišķi mainīt frekvences impulsu ieslēgšanas un izslēgšanas laiku, izmantojot divas diodes, kas kontrolē kondensatora uzlādes un izlādes laiku C1.

Diodes izolē abus parametrus un ļauj atsevišķi uzlādēt un izlādēt C1, izmantojot katla iestatījumus.

Tas savukārt ļauj diskrēti kontrolēt izejas PWM, izmantojot katla korekcijas. Šo iestatījumu varētu izmantot, lai precīzi kontrolētu līdzstrāvas motora apgriezienus ar minimāliem komponentiem.

Sprieguma dubultotājs, izmantojot NAND Gates

NAND vārti var tikt izmantoti arī, lai padarītu tos efektīvus sprieguma divkāršošanas ķēdes kā parādīts iepriekš. Nand N1 ir konfigurēts kā pulksteņa ģenerators vai frekvences ģenerators. Frekvence tiek pastiprināta un buferēta caur atlikušajiem 3 Nand vārtiem, kas ir vadīti paralēli.

Pēc tam izeja tiek ievadīta diodes kondensatora sprieguma divkāršotāja vai reizinātāja stadijā, lai beidzot veiktu 2X sprieguma līmeņa izmaiņas izejā. Šeit 5V tiek divkāršots līdz 10V, tomēr cits sprieguma līmenis ir līdz 15V maksimums, un to izmanto arī vajadzīgā sprieguma reizināšanas iegūšanai.

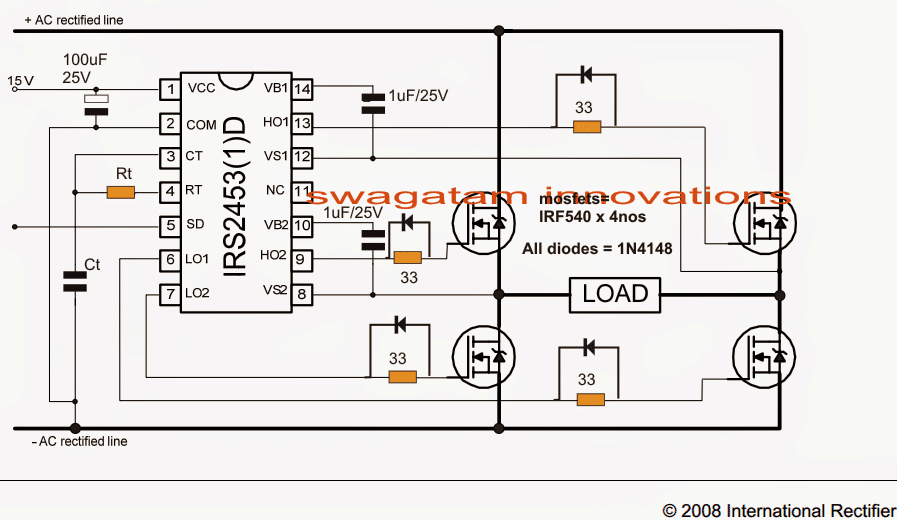

220 V pārveidotājs, izmantojot NAND Gates

Ja domājat, ka NAND gate var izmantot tikai zema sprieguma ķēžu veidošanai, iespējams, ka esat kļūdījies. Vienu 4011 IC var ātri pielietot, lai izveidotu jaudīgu 12V līdz 220V invertors kā parādīts iepriekš.

N1 vārti kopā ar RC elementiem veido pamata 50 Hz oscilatoru. RC daļas jāizvēlas atbilstoši, lai iegūtu paredzēto 50 Hz vai 60 Hz frekvenci.

N2 līdz N4 ir sakārtoti kā buferi un invertori tā, ka galīgā izeja tranzistoru pamatnēs rada pārmaiņus komutācijas strāvu vajadzīgajai spiediena vilkšanas darbībai uz transformatoru caur tranzistora kolektoriem.

Pjezo skaņas signāls

Tā kā NAND vārtus var konfigurēt kā efektīvus oscilatorus, saistītās lietojumprogrammas ir plašas. Viens no tiem ir pjezo skaņas signāls , kuru var uzbūvēt, izmantojot vienu 4011 IC.

NAND vārtu oscilatorus var pielāgot daudzu dažādu shēmu ideju īstenošanai. Šī ziņa vēl nav pabeigta, un pēc laika tas tiks papildināts ar vairākiem NAND vārtiem balstītiem dizainiem. Ja jums ir kaut kas interesants, kas saistīts ar NAND vārtu ķēdēm, lūdzu, dariet mums zināmu, ka jūsu atsauksmes tiks ļoti novērtētas.

Pāri: Sarkana LED LightStim shēma sejas grumbu noņemšanai Nākamais: Vienkārši divu tranzistoru projekti skolu skolēniem