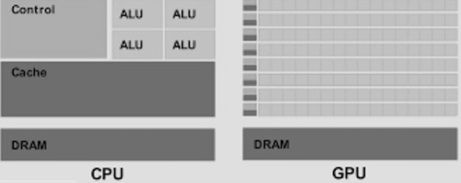

The kombinētās shēmas neizmantojiet nekāda veida atmiņu. Tāpēc agrākā ievades pozīcija neietver nekādus rezultātus attiecībā uz pašreizējo ķēdes situāciju. Lai gan secīgā ķēde ietver atmiņu, izeja ir atkarīga no ieejas, kas nozīmē, ka izeja var mainīties, pamatojoties uz ievadi. Šo ķēžu darbību var veikt, izmantojot iepriekšējo ķēdes ievadi, CLK, atmiņu un izvadi. Šajā rakstā ir apskatīts galvenā-verga flip flop pārskats. Bet pirms uzzināt par šo flip-flop, ir jāzina par pamatiem flip-flops piemēram, SR flip flop un JK flip flop.

Kas ir kapteiņa-verga flip flop?

Būtībā šāda veida flip flop var veidot ar diviem JK FF, savienojot virknē. Viens no šiem FF, viens FF darbojas kā kapteinis, kā arī citi FF darbojas kā vergs. Šo FF savienojumu var izdarīt šādi, galveno FF izeju var savienot ar vergu FF ieejām. Šeit vergu FF izejas var savienot ar galvenā FF ieejām.

Šāda veida FF invertoru tiek izmantots arī papildinājums diviem FF. Invertora savienojumu var veikt tā, lai kur apgriezto CLK impulsu varētu savienot ar vergu FF. Citiem vārdiem sakot, ja CLK impulss ir 0 galvenajam FF, tad CLK impulss būs 1 vergam FF. Līdzīgi, kad CLK impulss ir 1 galvenajam FF, tad CLK impulss būs 0 vergam FF.

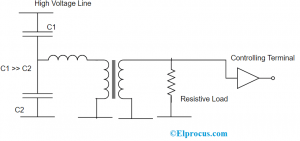

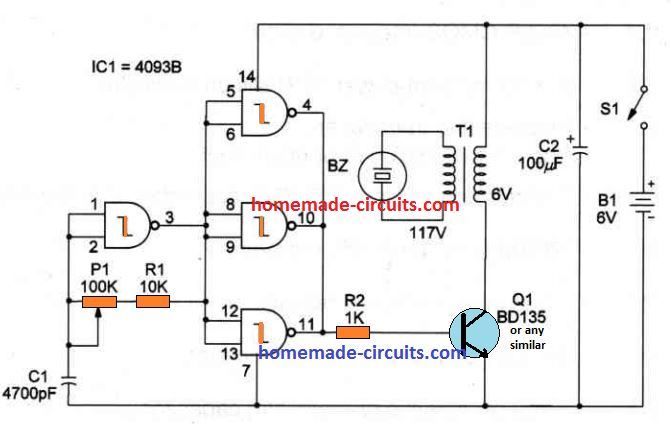

kapteinis-vergs-flip-flop-circuit

Master-Slave FF darbojas

Ikreiz, kad CLK impulss ir augsts, kas nozīmē 1, tad vergu var atdalīt. Ieejas, piemēram, J & K, var mainīt sistēmas stāvokli.

Vergu FF var atvienot, līdz CLK impulss samazinās līdz zemam līmenim, kas nozīmē 0. Kad CLK impulss atgriežas zemā stāvoklī, tad datus no galvenā FF var pārraidīt uz vergu FF un visbeidzot p var iegūt.

Sākumā galveno FF iedarbinās pozitīvā līmenī, bet vergu FF - negatīvā līmenī. Šī iemesla dēļ kapteinis FF atbild vispirms.

Ja J = 0 & K = 1, tad galvenā FF izeja ‘Q’ nonāk verga FF ieejā K un CLK piespiež vergu FF uz RST (atiestatīšana), tāpēc vergs FF kopē galveno FF.

Ja J = 1 & K = 0, tad galvenā FF ‘Q’ vērtība nonāk verga FF ieejā J un CLK negatīvā pāreja iestata vergu FF un kopē galveno.

Ja J = 1 & K = 1, tad tas pārslēdz CLK pozitīvo pāreju un tāpēc vergs pārslēdz CLK negatīvo pāreju.

Ja abi J & K ir 0, tad FF var nekustēt un Q paliek nekustīgs.

Laika diagramma

- Kad gan CLK impulss, gan o / p ir liels, tad tas paliek augsts līdz CLK ir zems stāvokļa dēļ.

- Pašlaik kapteiņa o / p pārvēršas par zemu, kad CLK impulss atkal pārvēršas par augstu un paliek zems, līdz CLK atkal pārvēršas par augstu.

- Tāpēc pārslēgšanās notiek CLK ciklā.

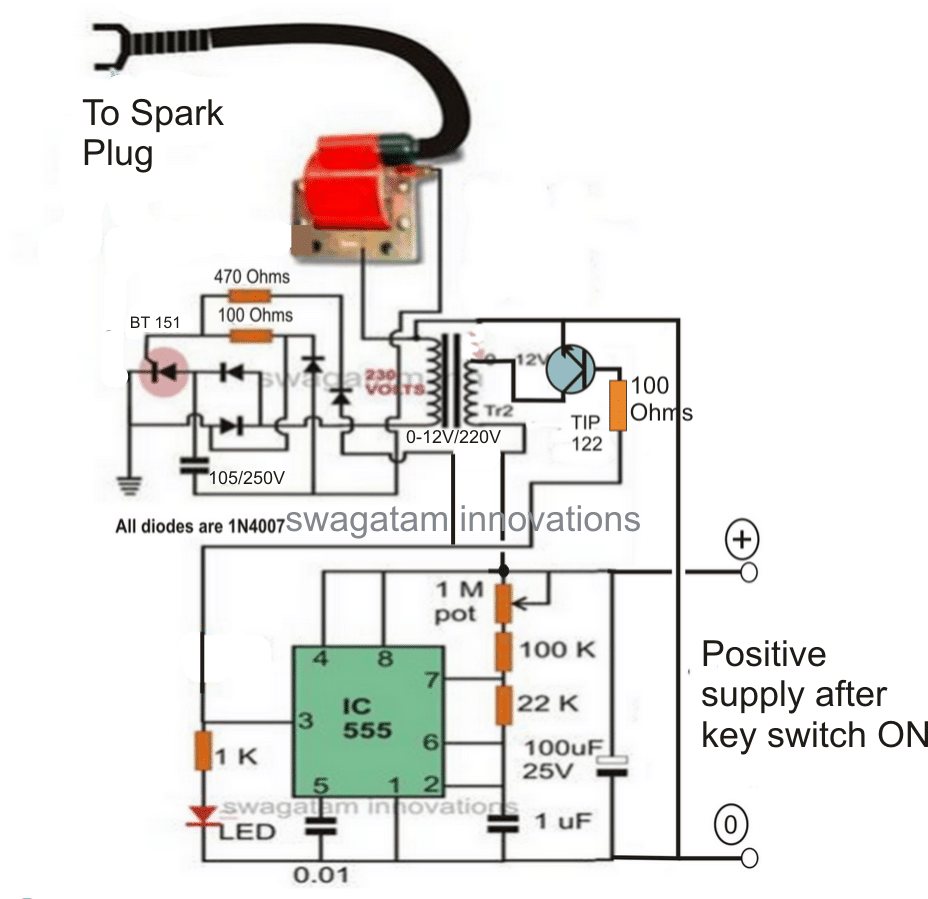

kapteiņa-verga-FF laika diagramma

- Ikreiz, kad CLK impulss ir 1, galvenais tiek iestatīts, nevis vergs, tāpēc vergs o / p paliek “0”, līdz CLK paliek 1.

- Kad CLK ir zems, vergs pārvēršas par darbību un paliek “1”, līdz CLK atkal pārvēršas par “0”.

- Pārslēgšanās notiek visas procedūras laikā, kamēr o / p mainās vienu reizi cikla laikā.

- Tas padara šo flip flop kā sinhronu aparātu, jo tas nodod tikai datus ar CLK signāla laiku.

Tādējādi tas viss attiecas uz Skolotāju-Vergu Flip Flop . No iepriekš minētās informācijas, visbeidzot, mēs varam secināt, ka šo FF var izveidot ar diviem FF, proti, galveno un vergu. Kad viens FF darbojas kā galvenā ķēde, tā aktivizējas virs CLK impulsa priekšējās malas. Līdzīgi, kad cits FF darbojas kā vergu ķēde, tas aktivizējas virs CLK impulsa krītošās malas.