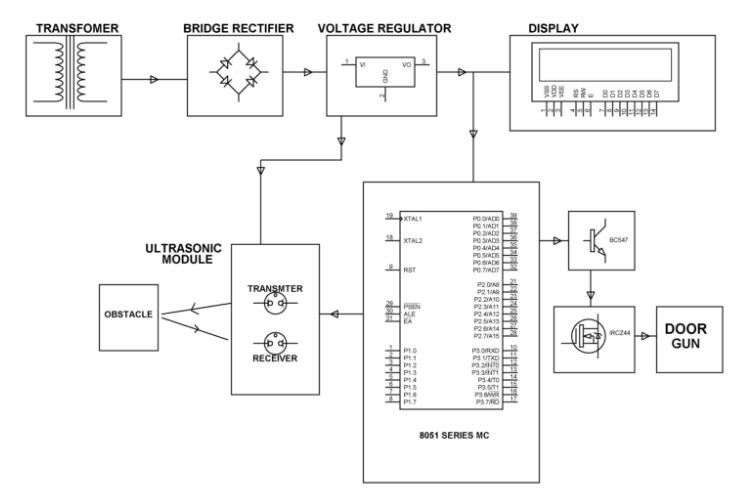

Bija laikmets, kad datori bija tik mamuta izmēra, ka, lai tos instalētu, viegli vajadzēja telpu. Bet šodien tie ir tik attīstījušies, ka mēs pat varam tos ērti pārnēsāt kā piezīmjdatorus. Jauninājums, kas to padarīja iespējamu, bija integrēto shēmu koncepcija. In Integrētās shēmas , liels skaits aktīvo un pasīvie elementi kopā ar to savstarpējiem savienojumiem tiek izstrādāti uz mazas silīcija plāksnītes, kuras šķērsgriezums parasti ir 50 līdz 50 mil. Šādu ķēžu ražošanā ievērotie pamatprocesi ietver epitaksiālo augšanu, maskētu piemaisījumu difūziju, oksīdu augšanu un oksīdu kodināšanu, modeļa izgatavošanai izmantojot fotolitogrāfiju.

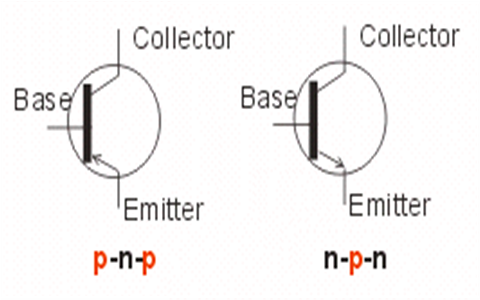

Komponentos virs vafeles ietilpst rezistori, tranzistori, diodes, kondensatori utt. Sarežģītākais elements, ko ražo virs IC, ir tranzistori. Transistori ir dažāda veida piemēram, CMOS, BJT, FET. Mēs izvēlamies tranzistora tehnoloģijas veidu, kas jāievieš virs IC, pamatojoties uz prasībām. Šajā rakstā ļaujiet mums iepazīties ar CMOS izgatavošana (vai) tranzistoru izgatavošana kā CMOS.

CMOS izgatavošana

Mazākai jaudas izkliedēšanas prasībai CMOS tehnoloģija tiek izmantots tranzistoru ieviešanai. Ja mums nepieciešama ātrāka shēma, tranzistori tiek ieviesti pāri IC izmantojot BJT . Izgatavošana CMOS tranzistori jo IC var veikt trīs dažādās metodēs.

N-well / P-well tehnoloģija, kur n-veida difūzija tiek veikta virs p-veida substrāta vai p-veida difūzija tiek veikta attiecīgi virs n-veida substrāta.

The Dvīņu aku tehnoloģija , kur NMOS un PMOS tranzistors tiek veidoti virs vafeles, vienlaikus veicot difūziju virs epitaksijas augšanas bāzes, nevis uz substrāta.

Silīcija On Insulator process, kurā silīcija kā substrāta vietā tiek izmantots izolatora materiāls, lai uzlabotu ātrumu un jutību pret aizķeršanos.

N - labi / P - labi tehnoloģija

CMOS var iegūt, integrējot abus NMOS un PMOS tranzistori pa to pašu silīcija vafeļu. N-urbuma tehnoloģijā n-veida urbums ir izkliedēts uz p-veida pamatnes, turpretī P-urbumā tas ir otrādi.

CMOS izgatavošanas darbības

The CMOS izgatavošanas process plūsma tiek veikts, izmantojot divdesmit pamata ražošanas posmus, bet ražots, izmantojot N-well / P-well tehnoloģiju.

CMOS izgatavošana, izmantojot N urbumu

1. darbība: Vispirms mēs izvēlamies substrātu kā pamatu izgatavošanai. N-urbumam tiek izvēlēts P veida silīcija substrāts.

Substrāts

2. solis - oksidēšana: N-veida piemaisījumu selektīvo difūziju veic, izmantojot SiO2 kā barjeru, kas aizsargā vafeļu daļas pret substrāta piesārņošanu. SiOdivitiek izklāstīts oksidēšanas procesā, pakļaujot substrātu augstas kvalitātes skābeklim un ūdeņradim oksidācijas kamerā aptuveni 10000c

Oksidēšana

3. solis - fotorezista audzēšana: Šajā posmā, lai atļautu selektīvu kodināšanu, SiO2 slānis tiek pakļauts fotolitogrāfijas procesam. Šajā procesā vafeles pārklāj ar viendabīgu gaismjutīgas emulsijas plēvi.

Fotorezista audzēšana

4. solis - maskēšana: Šis solis ir fotolitogrāfijas procesa turpinājums. Šajā solī tiek izveidots vēlamais atvērtības modelis, izmantojot trafaretu. Šis trafarets tiek izmantots kā maska virs fotorezista. Tagad substrāts ir pakļauts UV stari fotorezists, kas atrodas zem maskas atklātajiem reģioniem, tiek polimerizēts.

Fotorezista maskēšana

5. solis - Neeksponēta fotorezista noņemšana: Maska tiek noņemta un eksponētais fotorezista reģions tiek izšķīdināts, izveidojot vafeļu, izmantojot ķīmisku vielu, piemēram, trihloretilēnu.

Fotorezista noņemšana

6. solis - kodināšana: Plātne tiek iegremdēta fluorūdeņražskābes kodināšanas šķīdumā, kas noņem oksīdu no apgabaliem, pa kuriem difundē piedevas.

SiO2 kodināšana

7. solis - visa fotorezista slāņa noņemšana: Laikā kodināšanas process , tās SiO2 daļas, kuras aizsargā fotorezista slānis, netiek ietekmētas. Fotorezista maska tagad tiek noņemta ar ķīmisku šķīdinātāju (karstu H2SO4).

Fotorezista slāņa noņemšana

8. solis - N-urbuma veidošana: N-veida piemaisījumi tiek izkliedēti p-veida substrātā caur pakļauto reģionu, tādējādi veidojot N-urbumu.

N-urbuma veidošanās

9. solis - SiO2 atdalīšana: SiO2 slānis tagad tiek noņemts, izmantojot fluorūdeņražskābi.

SiO2 atdalīšana

10. solis - polisilīcija nogulsnēšana: A. Vārtu neatbilstība CMOS tranzistors radītu nevēlamu kapacitāti, kas varētu kaitēt ķēdei. Tāpēc, lai novērstu šo “pašizlīdzināto vārtu procesu”, priekšroka jādod, ja vārtu reģioni tiek veidoti pirms avota un notekas veidošanās, izmantojot jonu implantāciju.

Polisilīcija nogulsnēšanās

Polisilīciju izmanto vārtu veidošanai, jo tas var izturēt augsto temperatūru, kas pārsniedz 80000c, ja vafeles tiek pakļautas atlaidināšanas metodēm avota un notekas veidošanai. Polisilīcijs tiek nogulsnēts, izmantojot Ķīmiskās nogulsnēšanas process pār plānu vārtu oksīda slāni. Šis plāno vārtu oksīds zem polisilīcija slāņa novērš turpmāku dopingu zem vārtu reģiona.

11. solis - Vārtu reģiona izveidošana: Izņemot divus reģionus, kas nepieciešami, lai izveidotu vārtus NMOS un PMOS tranzistori atlikušo polisilīcija daļu noņem.

Vārtu reģiona veidošanās

12. solis - oksidēšanās process: Virs plāksnes tiek nogulsnēts oksidācijas slānis, kas turpmāk darbojas kā vairogs difūzijas un metalizācijas procesi .

Oksidācijas process

13. solis - maskēšana un difūzija: Lai veidotu reģionus n-veida piemaisījumu difūzijai, izmantojot maskēšanas procesu, tiek izveidotas nelielas atstarpes.

Maskēšana

Izmantojot difūzijas procesu, NMOS terminālu veidošanai tiek izstrādāti trīs n + reģioni.

N-difūzija

14. solis - oksīda atdalīšana: Oksīda slānis tiek noņemts.

Oksīda atdalīšana

15. solis - P tipa difūzija: Līdzīgi n tipa difūzijai PMOS termināļu veidošanai tiek veikta p tipa difūzija.

P tipa difūzija

16. solis - bieza lauka oksīda ieklāšana: Pirms metāla spailju veidošanas tiek uzklāts biezs lauka oksīds, kas veido aizsargslāni vafeļu reģioniem, kur nav nepieciešami spailes.

Biezs lauka oksīda slānis

17. solis - metalizācija: Šis solis tiek izmantots metāla termināļu veidošanai, kas var nodrošināt savstarpēju savienojumu. Alumīnijs ir izkliedēts uz visas vafeles.

Metalizācija

18. solis - liekā metāla noņemšana: Metāla pārpalikums tiek noņemts no vafeles.

19. solis - Termināļu veidošana: Spraugās, kas izveidojušās pēc liekā metāla noņemšanas, starpsavienojumiem tiek veidoti spailes.

Termināļu veidošana

20. solis - termināļu nosaukumu piešķiršana: Vārdi tiek piešķirti NMOS un PMOS tranzistori .

Termināļu nosaukumu piešķiršana

CMOS izgatavošana, izmantojot P well Technology

P-urbuma process ir līdzīgs N-urbuma procesam, izņemot to, ka šeit tiek izmantots n-veida substrāts un tiek veiktas p-veida difūzijas. Vienkāršības labad parasti dod priekšroku N akas procesam.

CMOS divu cauruļu izgatavošana

Izmantojot divu cauruļu procesu, var kontrolēt P un N tipa ierīču pastiprinājumu. Dažādi programmā iesaistītie soļi CMOS izgatavošana izmantojot Twin-tube metodi ir šādi

- Tiek paņemts viegli leģēts n vai p veida substrāts un tiek izmantots epitaksiālais slānis. Epitaksiālais slānis aizsargā mikroshēmas aizķeršanās problēmu.

- Audzē augstas tīrības pakāpes silīcija slāņus ar izmērītu biezumu un precīzu piedevu koncentrāciju.

- Cauruļu veidošana P un N urbumam.

- Plāna oksīda konstrukcija aizsardzībai pret piesārņojumu difūzijas procesu laikā.

- Avots un notece tiek veidoti, izmantojot jonu implantēšanas metodes.

- Izgriezumi tiek veikti porciju izgatavošanai metāla kontaktiem.

- Metalizācija tiek veikta metāla kontaktu vilkšanai

CMOS IC izkārtojums

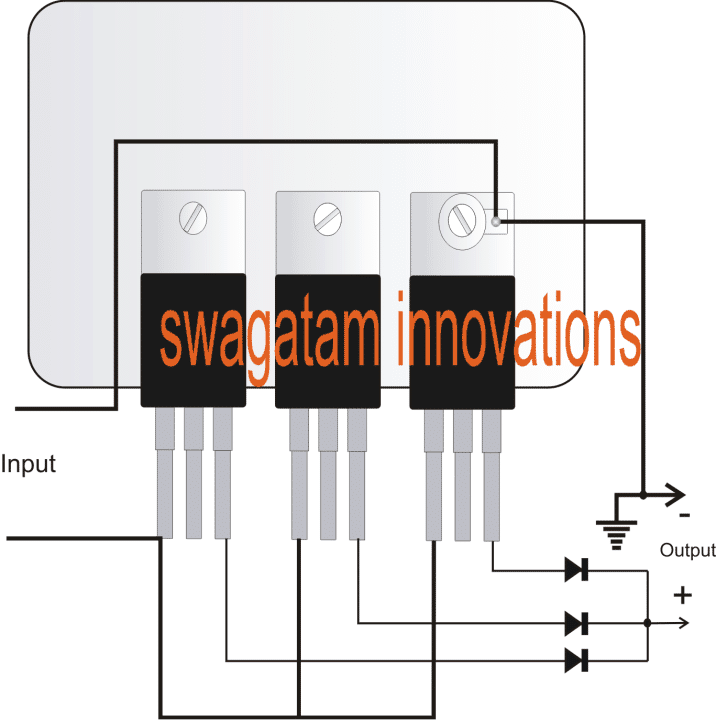

Augšējais skats uz CMOS izgatavošana un izkārtojums ir dots. Šeit var skaidri redzēt dažādus metāla kontaktus un N urbumu difūzijas.

CMOS IC izkārtojums

Tādējādi tas ir viss CMOS ražošanas paņēmieni . Apsvērsim vienu kvadrātveida vafeļu, kas sadalīta 400 mikroshēmās ar virsmas laukumu 50 mil ar 50 mil. Tranzistora izgatavošanai nepieciešams 50 mil2 laukums. Tādējādi katrā IC ir 2 tranzistori, tādējādi uz katras plāksnes ir uzbūvēti 2 x 400 = 800 tranzistori. Ja katrā partijā tiek apstrādāti 10 vafeles, vienlaikus var izgatavot 8000 tranzistorus. Kādas ir dažādas sastāvdaļas, kuras esat novērojis IC?