Digitālās aparatūras projektēšanas process pēdējos gados ir intensīvi pārveidojies. Tātad nelielas digitālās shēmas var ieviest, izmantojot PAL un PLA. Katra ierīce tiek izmantota ieviest dažādas shēmas kurām nav nepieciešams vairāk par konkrētajā mikroshēmā piedāvāto i / ps, o / ps un produktu terminu skaitu. Šīs mikroshēmas ir neatbilstošas diezgan pieticīgiem izmēriem, parasti atbalstot savstarpēju ieeju un izeju skaitu, kas nepārsniedz 32. Lai izveidotu šīs shēmas, kurām nepieciešams vairāk ieeju un izeju, var izmantot vai nu daudzus PLA / PAL, vai arī klasiskāku tipu mikroshēmu var izmantot ar nosaukumu CPLD (sarežģīta programmējama loģikas ierīce). CPLD mikroshēmā ir vairāki ķēdes bloki vienā mikroshēmā ar iekšējiem elektroinstalācijas resursiem ķēžu bloku piestiprināšanai. Katrs ķēdes bloks ir salīdzināms ar PLA vai PAL.

Kas ir sarežģīta programmējama loģiskā ierīce?

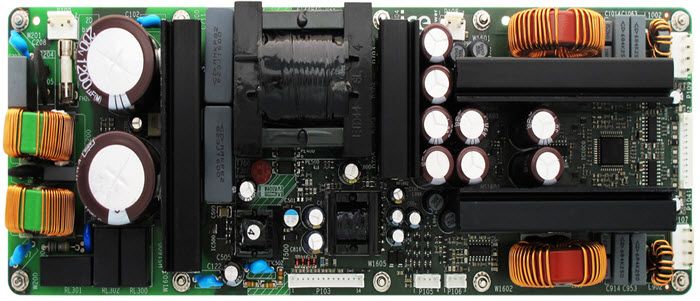

CPLD saīsinājums ir “Kompleksas programmējamās loģiskās ierīces”, tas ir viens integrētās shēmas veids ka lietojumprogrammu dizaineri izstrādā digitālās aparatūras, piemēram, mobilo tālruņu, ieviešanu. Tie var apstrādāt apzināti augstākus dizainus nekā SPLD (vienkāršas programmējamas loģikas ierīces), bet piedāvā mazāk loģikas nekā FPGA ( lauka programmējamie vārtu bloki ). CPLD ietver daudzus loģiskos blokus, un katrā no tiem ir 8-16 makroelementi. Tā kā katrs loģiskais bloks izpilda noteiktu funkciju, visas loģiskā bloka makro šūnas ir pilnībā savienotas. Atkarībā no lietošanas šie bloki var būt savienoti vai nebūt savienoti viens ar otru.

Sarežģīta programmējama loģiskā ierīce

Lielākajai daļai CPLD (sarežģītas programmējamas loģiskās ierīces) ir makrocellas ar loģisko funkciju summu un izvēles FF (flip-flop) . Atkarībā no mikroshēmas kombinatoriskās loģikas funkcija atbalsta no 4 līdz 16 produktu nosacījumiem ar iekļaujošu ventilatoru. CPLD atšķiras arī pēc maiņu reģistriem un loģiskajiem vārtiem. Šī iemesla dēļ FPGA vietā var izmantot CPLD ar lielu skaitu loģisko vārtu. Cita CPLD specifikācija norāda to produktu terminu skaitu, kurus var izpildīt makrocellas. Produkta noteikumi ir digitālo signālu rezultāts, kas izpilda noteiktu loģisko funkciju.

CPLD ir pieejami vairākās IC pakotņu formās un loģikas saimes. CPLD atšķiras arī pēc barošanas sprieguma, darba strāvas, gaidīšanas strāvas un jaudas izkliedes. Turklāt tos var iegūt ar dažādu atmiņas apjomu un dažāda veida atmiņu. Parasti atmiņa tiek izteikta bitos / megabitos. Atmiņas atbalsts sastāv no ROM, RAM un divu portu RAM. Tas ietver arī CAM (adresējama satura atmiņa), kā arī FIFO (pirmā ieeja, pirmā izeja) atmiņu un LIFO (pēdējā ienākošā, pēdējā izejošā) atmiņu.

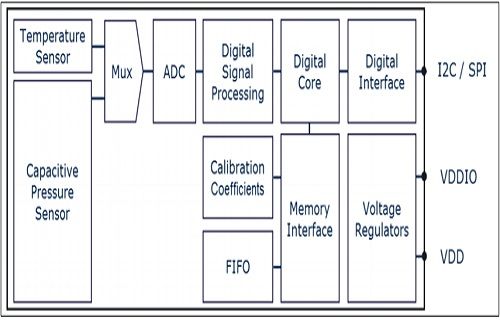

Kompleksi programmējamas loģiskās ierīces arhitektūra

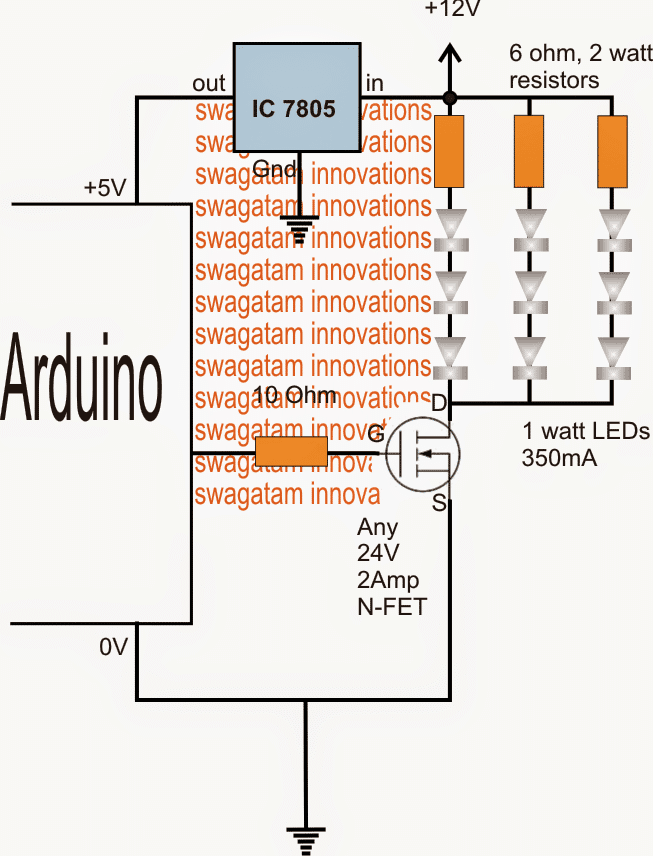

Sarežģīta programmējama loģiskā ierīce sastāv no programmējamu FB (funkcionālo bloku) grupas. Šo funkcionālo bloku ieejas un izejas ir savienotas kopā ar GIM (globālā starpsavienojuma matrica). Šī savienojuma matrica ir pārkonfigurējama, lai mēs varētu modificēt kontaktus starp funkcionālajiem blokiem. Būs daži ievades un izvades bloki, kas ļaus mums apvienot CPLD ar ārējo pasauli. CPLD arhitektūra ir parādīta zemāk.

Parasti programmējamais FB izskatās kā loģisko vārtu masīvs , kur var ieprogrammēt AND vārtu masīvu un OR vārti ir stabili. Bet katram ražotājam ir savs domāšanas veids, lai izstrādātu funkcionālo bloku. Uzskaitīto o / p var atrast, darbinot atgriezeniskās saites signālus, kas iegūti no OR vārtu izejām.

CPLD arhitektūra

CPLD programmēšanā dizains vispirms tiek kodēts Verilog vai VHDL valodā, tiklīdz kods ir (simulēts un sintezēts. Sintēzes laikā tiek izvēlēts CPLD modelis (mērķa ierīce) un tiek izveidots uz tehnoloģijām balstīts kartēšanas tīkla saraksts. Šis saraksts var būt tuvu - atbilstība oriģinālajai CPLD arhitektūrai, izmantojot vietas un maršruta procesu, kas parasti tiek panākts ar uzņēmuma CPLD uzņēmuma programmatūru vietas un maršruta programmatūrai. Tad operators veiks dažus apstiprināšanas procesus. Ja viss ir labi, viņš izmantos CPLD, citādi viņš to pārkārtos.

CPLD arhitektūras jautājumi

Apsverot sarežģītu programmējamu loģisko ierīci izmantošanai projektēšanā, var ņemt vērā dažus šādus arhitektūras jautājumus

- Programmēšanas tehnoloģija

- Funkciju bloķēšanas spēja

- I / O spēja

Daži no dažādu mazumtirgotāju CPLD ģimenēm ietver

- Altera MAX 7000 un MAX 9000 ģimenes

- ATMEL ATF un ATV ģimenes

- Režģis ir LSI ģimene

- Režģu (Vantis) MACH ģimene

- Xilinx XC9500 ģimene

CPLD ģimenes

CPLD pieteikumi

CPLD lietojumprogrammās ir šādas

- Sarežģītas programmējamas loģiskās ierīces ir ideāli piemērotas augstas veiktspējas, kritiskām vadības lietojumprogrammām.

- CPLD var izmantot digitālos dizainos, lai veiktu sāknēšanas iekrāvēja funkcijas

- CPLD izmanto lauka programmējamo vārtu masīva konfigurācijas datu ielādēšanai no gaistošās atmiņas.

- Parasti tos izmanto nelielās dizaina lietojumprogrammās, piemēram, adrešu dekodēšanā

- CPLD bieži izmanto daudzās lietojumprogrammās, piemēram, ar izmaksu ziņā jutīgām, ar akumulatoru darbināmām pārnēsājamām ierīcēm, jo tās ir mazas un tās lieto maz.

Tādējādi tas viss attiecas uz sarežģītu programmējamu loģisko ierīču arhitektūru un tās lietojumiem. Mēs ceram, ka esat labāk izpratis šo koncepciju. Turklāt visi jautājumi par šo koncepciju vai jebkuru elektrisko un elektronisko projektu īstenošanai , lūdzu, sniedziet vērtīgus ieteikumus, komentējot komentāru sadaļā zemāk. Šeit ir jautājums jums, kāda ir atšķirība starp CPLD un FPGA?

Foto kredīti:

- CPLD wikimedia

- CPLD arhitektūra slidesharecdn