Paritātes ģeneratora un paritātes pārbaudītāja galvenā funkcija ir atklāt kļūdas datu pārraidē, un šī koncepcija ir ieviesta 1922. gadā. RAID tehnoloģijā paritātes bits un paritātes pārbaudītājs tiek izmantoti, lai pasargātu no datu zaudēšanas. Paritātes bits ir papildu bits, kas pārraides pusē ir iestatīts uz “0” vai “1”, to izmanto, lai noteiktu tikai viena bita kļūdas, un tā ir vienkāršākā metode kļūdu noteikšanai. Kļūdu noteikšanai tiek izmantoti dažādi kļūdu noteikšanas kodi: paritāte, zvana skaitītājs, bloka paritātes kods, Hamminga kods, biquinary utt. Īss paskaidrojums paritātes bitu, paritāti ģenerators un pārbaudītājs ir izskaidroti turpmāk.

Kas ir paritātes bits?

Definīcija: Paritātes bits vai pārbaudes bits ir biti, kas pievienoti binārajam kodam, lai pārbaudītu, vai konkrētais kods ir paritātē vai nē, piemēram, vai kods ir pāra paritātē vai nepāra paritāte tiek pārbaudīts ar šo pārbaudes bitu vai paritātes bitu. Paritāte nav nekas cits kā 1 skaits, un ir divu veidu paritātes biti, kas ir pāra un nepāra biti.

Nepāra paritātes kodā kodam jābūt nepāra skaitā 1, piemēram, mēs ņemam 5 bitu kodu 100011, tiek teikts, ka šis kods ir nepāra paritāte, jo mūsu paņemtajā kodā ir trīs 1 skaitļi . Pāra paritātes bitā kodam jābūt pāra skaitā 1, piemēram, mēs ņemam 6 bitu kodu 101101, šis kods tiek uzskatīts par vienmērīgu paritāti, jo mūsu ņemtajā kodā ir četri 1 skaitļi

Kas ir paritātes ģenerators?

Definīcija: Paritātes ģenerators ir kombinēta ķēde pie raidītāja, tas ņem sākotnējo ziņojumu kā ievadi un ģenerē paritātes bitu šim ziņojumam, un raidītājs šajā ģeneratorā pārraida ziņojumus kopā ar paritātes bitu.

Paritātes ģeneratora veidi

Šī ģeneratora klasifikācija ir parādīta zemāk redzamajā attēlā

paritātes ģeneratora veidi

Pat Paritātes ģenerators

Pāra paritātes ģenerators uztur bināros datus pāra skaitā 1, piemēram, ņemtie dati ir nepāra skaitā 1, šis pāra paritātes ģenerators saglabās datus kā pāra skaitli 1, nepāra skaitam pievienojot papildu 1 1 skaits. Šī ir arī kombinēta shēma, kuras izeja ir atkarīga no dotajiem ievades datiem, kas nozīmē, ka ievadītie dati ir bināri dati vai binārs kods, kas norādīts paritātes ģeneratoram.

Apskatīsim trīs ieejas bināros datus, ka trīs biti tiek uzskatīti par A, B un C. Mēs varam uzrakstīt 23kombinācijas, izmantojot trīs ieejas bināros datus, kas ir no 000 līdz 111 (0 līdz 7), kopā astoņas kombinācijas iegūs no dotajiem trim ievadītajiem binārajiem datiem, kurus mēs esam apsvēruši. Trīs ieejas bināro datu pat paritātes ģeneratora patiesības tabula ir parādīta zemāk.

0 0 0 - Šajā ievades binārā kodā vienmērīgā paritāte tiek uzskatīta par “0”, jo ievade jau ir vienādā paritātē, tāpēc šai ievadei nav vēlreiz jāpievieno vienmērīga paritāte.

0 0 1 - - Šajā ievades binārā kodā ir tikai viens skaitlis “1”, un šis vienīgais skaitlis “1” ir nepāra skaitlis “1”. Ja ir nepāra skaitlis “1”, tad pat paritātes ģeneratoram ir jāveido vēl viens “1”, lai to padarītu par vienmērīgu paritāti, tāpēc vienmērīgu paritāti uzskata par 1, lai 0 0 1 kods būtu vienāds.

0 1 0 - Šis bits ir nepāra paritātē, tāpēc pāra paritāte tiek uzskatīta par 1, lai 0 1 0 kods kļūtu par paritāti.

0 1 1 - Šis bits jau ir vienādā paritātē, tāpēc vienmērīga paritāte tiek uzskatīta par 0, lai 0 1 1 kods būtu vienmērīgs.

1 0 0 - Šis bits ir nepāra paritātē, tāpēc pāra paritāte tiek uzskatīta par 1, lai 1 0 0 kods kļūtu par paritāti.

1 0 1 - Šis bits jau ir vienādā paritātē, tāpēc vienmērīgā paritāte tiek uzskatīta par 0, lai 1 0 1 kods būtu vienmērīgs.

1 1 0 - Šis bits ir arī vienmērīgā paritātē, tāpēc vienmērīgā paritāte tiek uzskatīta par 0, lai 1 1 0 kods būtu vienmērīgs.

1 1 1 - Šis bits ir nepāra paritātē, tāpēc pāra paritāte tiek uzskatīta par 1, lai 1 1 1 kods būtu vienāds.

Pat Paritātes ģeneratora patiesības tabula

| A B C | Pat Paritāte |

| 0 0 0 | 0 |

| 0 0 1 | 1 |

| 0 1 0 | 1 |

| 0 1 1 | 0 |

| 1 0 0 | 1 |

| 1 0 1 | 0 |

| 1 1 0 | 0 |

| 1 1 1 | 1 |

Karnaugh kartes (k-map) vienkāršošana trīsbitu ievadei ir vienāda

k-karte-pat-paritātes ģeneratoram

No iepriekš minētās pat paritātes patiesības tabulas paritātes bitu vienkāršotā izteiksme tiek rakstīta kā

Vienmērīga paritātes izteiksme, kas ieviesta, izmantojot divus Ex-OR vārtus, un šīs pat paritātes loģiskā diagramma, izmantojot Ex-OR loģikas vārti ir parādīts zemāk.

pat-paritāte-loģika-ķēde

Tādā veidā vienmērīgas paritātes ģenerators, izmantojot ievades datus, ģenerē pāra skaitli 1.

Nepāra paritātes ģenerators

Nepāra paritātes ģenerators saglabā bināros datus nepāra skaitā 1, piemēram, ņemtie dati ir pāra skaitā 1, šis nepāra paritātes ģenerators saglabās datus kā nepāra skaitli 1, pievienojot papildu 1 pāra skaitlis 1. Šī ir kombinētā shēma, kuras izeja vienmēr ir atkarīga no dotajiem ievades datiem. Ja ir pāra skaitlis 1, tiek pievienots tikai paritātes bits, lai bināro kodu padarītu par nepāra skaitli 1.

Apskatīsim trīs ieejas bināros datus, ka trīs biti tiek uzskatīti par A, B un C. Turpmāk parādīta nepāra paritātes ģeneratora patiesības tabula trim ieejas binārajiem datiem.

0 0 0 - Šajā ievades binārā kodā nepāra paritāte tiek uzskatīta par “1”, jo ievade ir pāra paritātē.

0 0 1 - Šī binārā ievade jau ir nepāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 0.

0 1 0 - Šī binārā ievade ir arī nepāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 0.

0 1 1 - Šis bits ir pāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 1, lai padarītu 0 1 1 kodu nepāra paritāti.

1 0 0 - Šis bits jau ir nepāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 0, lai 1 0 0 kods kļūtu par nepāra paritāti.

1 0 1 - Šis ievades bits ir pāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 1, lai 1 0 1 kods kļūtu par nepāra paritāti.

1 1 0 - Šis bits ir pāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par 1.

1 1 1 - Šis ievades bits ir nepāra paritātē, tāpēc nepāra paritāte tiek uzskatīta par o.

Nepāra paritātes ģeneratora patiesības tabula

| A B C | Nepāra paritāte |

| 0 0 0 | 1 |

| 0 0 1 | 0 |

| 0 1 0 | 0 |

| 0 1 1 | 1 |

| 1 0 0 | 0 |

| 1 0 1 | 1 |

| 1 1 0 | 1 |

| 1 1 1 | 0 |

Kavanaugh kartes (k-map) vienkāršošana trīs bitu ievades nepāra paritātei ir

k-map-par-nepāra-paritātes ģeneratoru

No iepriekš minētās nepāra paritātes patiesības tabulas paritātes bitu vienkāršotā izteiksme tiek rakstīta kā

Šī nepāra paritātes ģeneratora loģiskā diagramma ir parādīta zemāk.

loģika-ķēde

Tādā veidā nepāra paritātes ģenerators, izmantojot ievades datus, ģenerē nepāra skaitli 1.

Kas ir paritātes pārbaude?

Definīcija: Kombinētā ķēde pie uztvērēja ir paritātes pārbaudītājs. Šis pārbaudītājs uztver saņemto ziņojumu, ieskaitot paritātes bitu, kā ievadi. Tas dod izeju “1”, ja ir atrasta kļūda, un dod rezultātu “0”, ja ziņojumā, ieskaitot paritātes bitu, netiek atrasta kļūda.

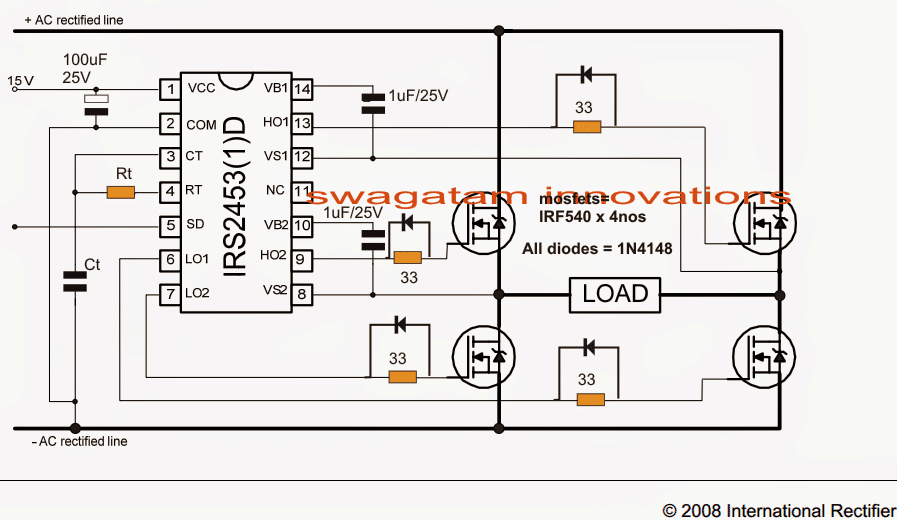

Paritātes pārbaudītāja veidi

Paritātes pārbaudītāja klasifikācija ir parādīta zemāk redzamajā attēlā

paritātes pārbaudītāja veidi

Pat Paritātes pārbaudītājs

Vienmērīgā paritātes pārbaudītājā, ja kļūdas bits (E) ir vienāds ar ‘1’, tad mums ir kļūda. Ja kļūdas bits E = 0 norāda, ka kļūdas nav.

Kļūdas bits (E) = 1, rodas kļūda

Kļūdas bits (E) = 0, nav kļūdas

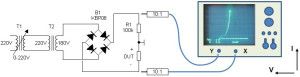

Paritātes pārbaudītāja ķēde ir parādīta zemāk redzamajā attēlā

loģika-ķēde

Nepāra paritātes pārbaudītājs

Nepāra paritātes pārbaudītājā, ja kļūdas bits (E) ir vienāds ar “1”, tad tas norāda, ka kļūdas nav. Ja kļūdas bits E = 0 norāda, ka ir kļūda.

Kļūdas bits (E) = 1, nav kļūdas

Kļūdas bits (E) = 0, rodas kļūda

Paritātes pārbaudītājs nevarēs noteikt, vai kļūdas ir vairāk par ‘1’ bitiem, un arī datu pareizība nav iespējama. Šie ir galvenie paritātes pārbaudītāja trūkumi.

Paritātes ģenerators / pārbaudītājs, izmantojot IC

IC 74180 veic paritātes ģenerēšanas funkciju, kā arī pārbaudi. 9 bitu (8 datu biti, 1 paritātes bits) paritātes ģenerators / pārbaudītājs ir parādīts zemāk redzamajā attēlā.

ic-74180

IC 74180 satur astoņus datu bitus (X0līdz X7), VDC,pāra ievade, nepāra ievade, septiņas izejas, S nepāra izeja un iezemētā tapa.

Ja dotā pāra un nepāra ieeja ir augsta (H), tad pāra un nepāra izejas abas ir zemas (L), līdzīgi, ja dotās ieejas abas ir zemas (L), tad pāra un nepāra izejas abas kļūst augstas ( H).

Paritātes priekšrocības

Paritātes priekšrocības ir

- Vienkāršība

- Viegli izmantot

Pieteikumi paritātes

Paritātes pieteikumi ir

- In digitālās sistēmas un daudzās aparatūras lietojumprogrammās tiek izmantota šī paritāte

- Paritātes bits tiek izmantots arī mazo datorsistēmu saskarnē (SCSI) un arī perifēro komponentu starpsavienojumā (PCI), lai noteiktu kļūdas.

Bieži uzdotie jautājumi

1). Kāda ir atšķirība starp paritātes ģeneratoru un paritātes pārbaudītāju?

Paritātes ģenerators raidītājā ģenerē paritātes bitu, un paritātes pārbaudītājs pārbauda uztvērējā paritātes bitu.

2). Ko nenozīmē paritāte?

Ja paritātes bitus neizmanto kļūdu pārbaudei, paritātes bits tiek uzskatīts par nepopisku, bez paritātes vai paritātes neesamību.

3). Kāda ir paritātes vērtība?

Paritātes vērtības jēdziens, ko izmanto gan precēm, gan vērtspapīriem, un šis termins attiecas uz gadījumiem, kad abu aktīvu vērtība ir vienāda.

4). Kāpēc mums ir nepieciešams paritātes pārbaudītājs?

Paritātes pārbaudītājs ir nepieciešams, lai atklātu kļūdas komunikācijā, kā arī atmiņas glabāšanas ierīcēs testēšanai tiek izmantots paritātes pārbaudītājs.

5). Kā paritātes bits var atklāt bojātu datu vienību?

Šajā tehnikā lieko bitu sauc par paritātes bitu, tas nosaka bojātu datu vienību, kad datu pārsūtīšanas laikā rodas kļūda.

Šajā rakstā, kā paritāte ģenerators un pārbaudītājs ģenerē un pārbauda bitu, un tā veidi, loģiskās shēmas, patiesības tabulas un k-kartes izteiksmes tiek īsumā apskatītas. Šeit ir jautājums jums, kā aprēķināt pāra un nepāra paritāti?