Termins VLSI nozīmē “ļoti liela mēroga integrācijas tehnoloģija”, kas ietver integrētu shēmu (IC) projektēšanu, apvienojot tūkstošiem tranzistori loģiski vienā mikroshēmā dažādas loģiskās shēmas . Šīs mikroshēmas galu galā samazina aizņemtās ķēdes telpu, salīdzinot ar ķēdēm ar parastajiem IC. Skaitļošanas jauda un telpas izmantošana ir galvenie VLSI dizaina izaicinājumi. VLSI projektu īstenošana paver izaicinošu un gaišu karjeru studentiem, kā arī pētniekiem. Daži no jaunajiem VLSI populārajiem apgabaliem ir Laukā programmējams vārtu masīvs lietojumprogrammas (FPGA), ASIC dizainus un SOC. Turpmāk sniegts dažu VLSI projektu saraksts tiem studentiem, kuri nopietni meklē projektus šajā jomā. Šajā rakstā ir apskatīts VLSI projektu pārskats, kuru pamatā ir FPGA, Xilinx, IEEE, Mini, Matlab utt. Šie projekti ir ļoti noderīgi inženierzinātņu studentiem, M.tech studentiem.

VLSI projekti inženierzinātņu studentiem

VLSI projekti ar kopsavilkumiem elektronikas inženierzinātņu studentiem tiek apspriesti turpmāk.

VLSI projekti

1). Diskrētā viļņa pārveidošana, pamatojoties uz 3D pacelšanu

Šis projekts palīdz nodrošināt ļoti precīzus attēlus, izmantojot attēla kodēšanu, nezaudējot tā datus. Lai to panāktu, šis process ievieš pacelšanas filtru atkarībā no 3D diskrētā viļņa VLSI arhitektūras transformācijas.

2). SFQ reizinātāja projektēšana ar 4 bitu efektīvi, izmantojot ātrgaitas aparatūru

Šis projekts galvenokārt tiek izmantots modificēta kabīnes kodētāja (MBE) ieviešanai ar 4 bitu SFQ bāzes reizinātājs . Šis reizinātājs nodrošina labu veiktspēju, salīdzinot ar parasto kabīnes kodētāju. Šo projektu galvenokārt izmanto kritiskās kavēšanās lietojumos.

3). Kriptogrāfijas procesors, ko izmanto viedkartēs ar efektīvu platību

Šis projekts tiek izmantots, lai ieviestu trīs kriptogrāfijas algoritmus, kurus atbalsta gan privātās, gan publiskās atslēgas, kuras tiek izmantotas viedkarte lietojumprogrammas ārkārtīgi drošas lietotāju verifikācijas un datu nodrošināšanai komunikācija .

4). Ātrgaitas vai mazjaudas reizinātājs ar nepareizas jaudas samazināšanas metodi

Šī ierosinātā sistēma izslēdz aritmētisko vienību bezjēdzīgos viltus signālus, lai izvairītos no nevajadzīgas datu pārraides, kas neietekmē pēdējos skaitļošanas rezultātus. Šī sistēma izmanto SPST metodi pavairotājiem, lai panāktu mazjaudas un ātrgaitas datu pārraidi.

5). Bezzudumu datu algoritma saspiešana un dekompresēšana

Šis projekts galvenokārt tiek realizēts divpakāpju aparatūras arhitektūrai atkarībā no PDLZW (Parallel Dictionary LZW) algoritma funkcijas, kā arī Adaptīvā Huffmana tipa algoritma, ko izmanto gan bezzudumu datu saspiešanas, gan bezzudumu dekompresijas lietojumiem.

6). Turbo dekodera ar zemu sarežģītību arhitektūra energoefektīviem WSN

Piedāvātā sistēma tiek izmantota, lai samazinātu kopējo enerģijas patēriņu visā WSN datu pārraides laikā, izmantojot LUT-Log-BCJR sadalīšanās algoritmu uz pamata ACS (Add Compare Select) operācijām.

7). VLSI arhitektūra attēla impulsa trokšņa efektīvai noņemšanai

Šo piedāvāto sistēmu galvenokārt izmantoja, lai vizuāli uzlabotu attēla kvalitāti, lai izvairītos no iespējas tikt sabojātam ar impulsu troksni, lai ieviestu efektīvu VLSI arhitektūru ar malu saglabājoša filtra palīdzību.

8). Multivides saspiešanai izmantotā atmiņā esoša procesora arhitektūra

Šī ierosinātā sistēma nodrošina zemas sarežģītības arhitektūru a procesors atmiņā, lai atbalstītu multivides lietojumprogrammas, proti, attēlu saspiešanu, video, izmantojot milzīgas vienas instrukcijas, daudzu datu jēdzienus un instrukciju vārdu.

9). Laika sinhronizācijas tehnika ar simbolu ātrumu bezvadu OFDM sistēmām ar mazu jaudu

Šo piedāvāto sistēmu galvenokārt izmantoja, lai uzlabotu bezvadu OFDM darbību (Ortogonālā frekvenču nodaļa Multipleksēšana ) sistēmu, ar pulksteņa palīdzību samazinot visas pamatjoslas jaudu ģenerators ar fāzes noregulējamu un dinamisku parauga laika kontrolieri.

10). Uz akumulatoru balstīta mazjaudas un ātrgaitas reizinātāja ieviešana ar SPST Adder & Verilog

Šis projekts tiek izmantots, lai izstrādātu mazjaudas un ātrgaitas MAC (reizinātāju un akumulatoru), pieņemot kļūdainu jaudas nomākšanas metodi MBE (modificēts kabīnes kodētājs). Izmantojot šo dizainu, var novērst visas komutācijas jaudas izkliedi.

11). Robotu procesoru projektēšana un ieviešana, iespējojot sadursmju novēršanu ar RFID tehnoloģiju

Piedāvātā sistēma galvenokārt tiek izmantota robota procesora ieviešanai ar pret sadursmi, lai izvairītos no fiziskas robotu sadursmes daudzrobotu vidē. Šis algoritms galvenokārt tiek ieviests, izmantojot VHDL un RFID tehnoloģiju.

12). Loģiskās ķēdes projektēšana ar efektīvu enerģijas patēriņu, izmantojot adiabātisko metodi

Šī sistēma parāda loģisko ķēžu dizainu, efektīvi izmantojot adiabātisko metodi, salīdzinot ar parasto CMOS dizainu, izmantojot ķēdes, kas izmanto NAND & NOR vārti . Izmantojot adiabātisko metodi, enerģijas izkliedi tīklā var samazināt, kā arī pārstrādāt uzkrātajā kondensatorā uzkrāto enerģiju.

3). Šifrēšanas sistēma sistēmas skaitļošanas ātruma palielināšanai

Galvenais šī projekta mērķis ir uzlabot datu pārraides drošību, lai uzlabotu skaitļošanas ātrumu, ieviešot AES algoritmu, izmantojot FPGA. Tātad šo simulāciju, kā arī matemātisko dizainu var veikt ar VHDL koda palīdzību.

14). AHM vai uzlabotas augstas veiktspējas kopnes IP bloks

Šis projekts galvenokārt tiek izmantots, lai izstrādātu Advanced arhitektūru Mikrokontrolleris Autobuss (AMB), izmantojot AHBN (uzlaboto augstas veiktspējas autobusu). Šo projektu var noformēt ar VHDL kodu, ieviešot tādus blokus kā master & save.

15). DSM balstīts daudzmodu RF raiduztvērējs ar daudzkanālu

Šī sistēma galvenokārt tika izmantota daudzmodu raidītāja un uztvērēja arhitektūras un RF daudzkanālu projektēšanai ar Delta-Sigma modulatoru. Šī ierosinātā sistēma izmanto VHDL valodu, lai ieviestu divas arhitektūras.

16). Izslēgšanas slēdža koncentrators, izmantojot asinhrono pārsūtīšanas režīmu

Izmantojot šo projektu, ar tādu rīku palīdzību kā VHS un VHDL var izveidot izslēgšanas slēdzi, kura pamatā ir asinhronā pārsūtīšana. Šo izslēgšanas slēdzi var izmantot virtuālās shēmas pakešu tīklos, kā arī datagrammas lietojumprogrammās.

17). Asinhrono ķēžu uzvedības sintēze

Šis projekts galvenokārt tiek izmantots, lai nodrošinātu uzvedības sintēzes tehniku, ko izmanto asinhronajām shēmām. Abas veidnes, piemēram, balsa un asinhronās ieviešanas, ir galvenie dizaina elementi.

18). AMBA dizains, izmantojot atbilstošu AHB atmiņas kontrolieri

Šis projekts tiek izmantots, lai izstrādātu MC (atmiņas kontrolleri) atkarībā no AMBA (uzlabotas mikrokontrolleru kopņu arhitektūras) sistēmas atmiņas kontrolei, izmantojot galveno atmiņu, piemēram, SRAM un ROM.

19). Carry Tree Adder ieviešana

Pārnēsāšanas koku papildinātājs, kas balstīts uz VLSI dizainu, tiek saukts par labāko veiktspējas papildinātāju, salīdzinot ar parastajiem binārajiem papildinātājiem. Šī projekta īstenotāji ir koka, kogge akmens un reti kogge akmens.

20). CORDIC fiksēta leņķa rotācija, pamatojoties uz dizainu

Šīs ierosinātās sistēmas galvenā koncepcija ir vektoru pagriešana, izmantojot fiksētus leņķus. Šie leņķi ir nepieciešami spēlēm, robotikai, attēlu apstrāde utt. Izmantojot šo projektu, vektora rotāciju var panākt, izmantojot īpašus leņķus, izstrādājot CORDIC (koordinātu rotācijas digitālais dators).

21). FIR filtra dizains ar uzmeklēšanas tabulas sadalīto aritmētiku

Šī ierosinātā sistēma galvenokārt uzlabo FIR filtrs veiktspēju, noformējot to, izmantojot reizinātāja vietā trīsdimensiju uzmeklēšanas tabulas sadalītu aritmētiku. Tātad šo dizainu var ieviest, izmantojot tādas programmatūras kā FPGA un Xilinx.

22). Push-pull pulsējošās aizbīdņi ar ātrgaitas un zemas jaudas nosacījumiem

Šis projekts tiek izmantots, lai izpildītu energoefektīvas un augstas veiktspējas impulsveida aizbīdņus, kurus galvenokārt izmanto VLSI sistēmām, izmantojot jaunu topoloģiju. Tā kā šī topoloģija galvenokārt ir atkarīga no nobīdes pēdējā posmā, izmantojot divu dalīšanas joslu caur nosacītu impulsu ģeneratoru.

23). Aritmētiskā kodētāja VLSI arhitektūra SPIHT

Šī ierosinātā sistēma uzlabo aritmētiskās kodēšanas metodes caurlaidi, sadalot kopas hierarhisko koku (SPIHT) attēlu saspiešanā ar ātrgaitas arhitektūru atkarībā no FPGA.

24). EKG signāla trokšņu slāpēšana, pamatojoties uz FPGA

Šis projekts tiek izmantots, lai troksni ierobežotu EKG signālos, izmantojot divus vidējos filtrus ar attiecīgi 91 un 7 parauga punktu izmēriem. Tātad šo procesu var sasniegt, ieviešot FPGA dizains pamatojoties uz VHDL kodu.

25). VLSI balstīts augstas veiktspējas attēlu mērogošanas procesors ar zemām izmaksām

Šis projekts tiek izmantots, lai ieviestu algoritmu attēlu mērogošanas procesoram, kura pamatā ir VLSI ar mazāku atmiņu un augstu veiktspēju. Piedāvātais sistēmas dizains galvenokārt ietver filtru, pārkonfigurējamu dinamisko metožu un aparatūras koplietošanas apvienošanu, lai samazinātu izmaksas.

26). Sistoliskā masīva arhitektūras projektēšana un ieviešana efektīvi

Šī projekta galvenā koncepcija ir izstrādāt aparatūras modeli, ko izmanto sistoliskā masīva reizinātājam. Šo masīvu galvenokārt var izmantot, lai veiktu bināro reizināšanu ar VHDL platformas palīdzību. Piedāvāto sistēmas dizainu var īstenot, izmantojot FPGA & Isim programmatūru.

27). QPSK dizains un sintēze, izmantojot VHDL kodu

QPSK ir viena no galvenajām modulācijas metodēm. Šo metodi izmanto satelīta radio lietojumos. Šo modulācijas paņēmienu var ieviest, izmantojot atgriezeniskus loģiskos vārtus. QPSK tehnikas projektēšanu var veikt ar VHDL koda palīdzību.

28). DDR SDRAM kontroliera projektēšana un ieviešana ar lielu ātrumu

Piedāvātā sistēma tiek izmantota DDR SDRAM kontroliera projektēšanai, lai pārsūtītu pārsprāgtos datus atkarībā no liela ātruma, lai sinhronizētu šos datus starp iegultās sistēmas un DDR SDRAM shēmām. Izmantojot VHDL valodu, kodu var izstrādāt.

29). 32 bitu RISC procesoru projektēšana un ieviešana

Šī projekta galvenā koncepcija ir 32 bitu ieviešana RISC (samazināts instrukciju kopas dators) ar tāda rīka palīdzību kā XILINK VIRTEX4. Šajā projektā 16 instrukciju kopas ir izstrādātas visur, kur katru instrukciju var izpildīt vienā CLK ciklā, izmantojot piecfāžu cauruļvadu metodi.

30). Autobusu tilta ieviešana starp AHB un OCP

Piedāvātā sistēma tiek izmantota kopnes tilta projektēšanai starp diviem protokoliem, proti, kopēju un standarta. Sakaru protokoli, piemēram, AHB (uzlabotas augstas veiktspējas kopne) un OCP (atvērts kodola protokols), ir ļoti populāri, kurus izmanto SoC (sistēmas mikroshēma) .

VLSI Projektu idejas inženierzinātņu studentiem

Zemāk ir saraksts ar VLSI projektiem, kuru pamatā ir FPGA, MatLab, IEEE un Mini projekti inženierzinātņu studentiem.

VLSI projekti M. tehnikas studentiem

VLSI projektu sarakstā, kura pamatā ir M. Tech Students, ir šāds.

- Platības ziņā efektīvs un ļoti uzticams uz RHBD balstīts I0T atmiņas šūnu dizains, ko izmanto aviācijas un kosmosa lietojumprogrammās

- Fāžu detektors ar daudzlīmeņu pusrādi, ko izmanto CLK un datu atkopšanas ķēdēm

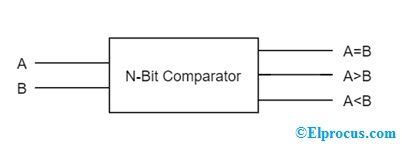

- Komparators ar mazu jaudu un lielu ātrumu, ko izmanto precīzām lietojumprogrammām

- Gated sprieguma līmeņa tulkotājs ar augstas veiktspējas un integrētu multipleksoru

- CNTFET bāzes trīslīmeņu papildinātājs ar augstu veiktspēju

- Lieluma salīdzinātāja dizains ar mazu jaudu

- Sliekšņa loģisko vārtu ar pašreizējo režīmu kavēšana kavējuma analīzei

- Jauktas loģikas līniju dekoderu dizains ar zemu jaudu un lielu veiktspēju

- Miega konvencijas loģikas pārbaudāmības dizains

- Sprieguma līmeņa pārslēdzējs dubultās piegādes lietojumprogrammām ar lielu ātrumu un enerģijas patēriņu

- Zemas jaudas un zemsprieguma dubultās astes salīdzinātāja dizains un analīze

- Flip-Flop dizains, kas balstīts uz impulsu, kas aktivizēts ar mazu enerģijas patēriņu, izmantojot signāla pārvades metodi

- Efektīva shēmu projektēšana, kuras pamatā ir izpildlaika pārkonfigurējami FET

- Lieluma salīdzinātāja dizains ar mazu jaudu

- Aizkavēta loģisko vārtu dizaina analīze ar pašreizējā režīma slieksni

The FPGA balstīti VLSI projekti inženierzinātņu studentiem un CMOS VLSI dizaina mini projekti ir uzskaitīti zemāk.

- SEU sacietēto shēmu dizains un raksturojums FPGA, pamatojoties uz SRAM

- Kompakts, uz Memristor balstīts CMOS hibrīda LUT dizains un potenciāls lietojums, ko izmanto FPGA

- FPGA ieviešana ar ultraskaņas sensoru palīdzību attāluma mērīšanai

- FPGA ieviešana stenda reizinātājam ar Spartan6 FPGA

- Diskrēta viļņu pārveidošana, kuras pamatā ir celšana ar Spartan3 FPGA

- ARM kontrolieris robotikā, izmantojot FPGA

- FPGA bāzes UART ar daudzkanālu

- EKG signāla trokšņu slāpēšana, izmantojot FPGA

- UTMI balstīta FPGA ieviešana un USB 2.0 protokola slānis

- Mediāna filtra ieviešana ar Spartan3 FPGA

- Uz AES algoritmu balstīta FPGA ieviešana

- Drošības trauksmes sistēma, kuras pamatā ir PIC, lai ieviestu FPGA ar Spartan 3an

- FPGA ieviešana tālvadības sistēmu kontroliera projektēšanai

- FPGA attēlu apstrādes komplekts, izmantojot lineāro un morfoloģisko attēlu filtrēšanu

- Spartan3 FPGA bāzes medicīniskās kodolsintēzes ieviešana

Saraksts VLSI mini projekti, izmantojot VHDL kodu ietver sekojošo.

- Salīdzinātājs ar lielu ātrumu, izmantojot VLSI

- Peldošā komata reizinātājs, izmantojot VLSI

- VLSI balstīta binārā konversija uz pelēko

- Digitālais filtrs

- CLK Gating, pamatojoties uz VLSI

- Vēdiskais reizinātājs

- CMOS FF, izmantojot VLSI

- Paralēlā procesora arhitektūra, izmantojot VLSI

- VLSI bāzes pilns papildinātājs

- DRAM / dinamiskās brīvpiekļuves atmiņas dizains, pamatojoties uz VLSI

- SRAM izkārtojums balstīts uz VLSI

- Digitālā signāla procesors, kas balstīts uz VLSI

- VLSI bāzes multipleksers

- MAC vienības projektēšana, pamatojoties uz VLSI

- VLSI balstīts diferencētājs

- VLSI balstīta FFT vai ātra Furjē pārveidošana

- Diskrētā kosinusa transformācijas arhitektūra, kuras pamatā ir VLSI

- 16 bitu reizinātāja dizains, izmantojot VLSI19

- VLSI balstīta FIFO bufera projektēšana

- Ātrgaitas akselerators, kas balstīts uz VLSI

VLSI projekti, izmantojot MATLAB un Xilinx

VLSI projektu, kuru pamatā ir MATLAB un VLSI projekti, izmantojot Xilinx, saraksts ietver sekojošo.

- CDMA modema dizains un analīze ar MATLAB

- FIR filtru dizains, izmantojot VHDL uz FPGA un MATLAB balstītas analīzes

- ModelSim & Matlab vai Simulink balstīta automobiļu inženierijas sistēmu simulācija

- Xilinx balstītie papildinātāji, piemēram, Ripple Carry & Carry Skip

- Aritmētiskā vienība, kuras pamatā ir 32 bitu peldošais punkts

- Peldošo punktu ALU

- RISC procesors, kas balstīts uz 32 bitu

- Ortogonālā koda konversijas spējas

- Tirdzniecības automāts Xilinx un Verilog

- Xilinx bāzes Parallel Prefix Adders ar 256 bitiem

- Protokols savstarpējai autentifikācijai, izmantojot Xilinx

- Piekļuves struktūra ar vienciklu loģikas pārbaudei, izmantojot Xilinx

- UTMI un protokola slānis, pamatojoties uz USB2.0, izmantojot Xilinx

- Datu saspiešanas un dekompresijas konfigurēšana, izmantojot Xilinx FPGA

- Xilinx 4000 bāzes BIST un Spartan sērijas FPGA

- IIR filtrs, pamatojoties uz MATLAB un VLSI

- FIR filtrs, izmantojot MATLAB

IEEE projekti

The IEEE VLSI projektu saraksts ir norādīts zemāk.

- VLSI balstīta bezvadu mājas automatizācijas sistēma, izmantojot Bluetooth

- Impulsu trokšņa noņemšana attēlā, izmantojot efektīvu VLSI arhitektūru

- Procesora atmiņā arhitektūra multivides saspiešanai

- Temperatūras sistēmas uzraudzība, izmantojot Cloud & IoT

- OFDM sistēmas ieviešana ar IFFT & FFT

- Kodu izstrāde un ieviešana ar Verilog

- Pirkstu nospiedumu atpazīšana, izmantojot VHDL, izmantojot Gabor filtru

- Aritmētisko funkciju atjaunošana ar ROM atkarībā no tuvināšanas pieejām

- Paritātes pārbaudes koda dekodētāja augstas efektivitātes un zemas blīvuma veiktspējas analīze mazjaudas lietojumprogrammās

- FFT arhitektūra ar cauruļvadu Radix-2k atgriezenisko saiti

- Flip-Flops dizains VLSI lietojumprogrammām, izmantojot CMOS tehnoloģiju ar augstu veiktspēju

- FIR filtra dizains ar uzmeklēšanas tabulu pēc sadalītās aritmētikas

- VLSI balstīts zemu izmaksu un uzlabots attēlu mērogošanas procesors

- ASIC Advance Turbo Encoder & Decoder ar 3GPP LTE ieviešana un dizains

- Push-pull pulsējošās aizbīdņi ar zemu jaudu un ātrgaitas nosacījumiem

- Uzlabota skenēšana zemas jaudas skenēšanas testēšanā

- Aritmētiskā kodētāja VLSI arhitektūra SPIHT

- VHDL ieviešana UART

- VLSI balstīts sprieguma regulators ar zemu izlaišanas spēju

- Flash ADC dizains ar uzlaboto salīdzinātāju shēmu

- Mazjaudas reizinātāja dizains ar saliktu pastāvīgas aizkaves loģikas stilu

- Double Tail Comparator ar augstas veiktspējas un mazu jaudu

- Flash atmiņas sistēma ar augstu veiktspēju atkarībā no rakstīšanas bufera un virtuālās atmiņas

- Mazjaudas FF, pamatojoties uz miega kaudzes pieeju

- LFSR enerģijas optimizācija mazjaudas BIST, kas ieviesta HDL

- Tirdzniecības automātu dizains un ieviešana ar Verilog HDL

- Akumulatora dizains balstīts uz trīs svara modeļa ģenerēšanu ar LP-LSFR

- Reed-Solomon dekoders ar ātrgaitas un zemas sarežģītības pakāpi

- Ātrāka Dadda reizinātāja projektēšanas tehnika

- Digitāls, uz demodulāciju balstīts FM radio uztvērējs

- Testa parauga ģenerēšana ar BIST shēmām

- VLSI arhitektūras ieviešana ar ātrgaitas cauruļvadu

- On-Chip Bus OCP protokola dizains, izmantojot kopnes funkcijas

- Fāzes frekvences detektors un uzlādes sūkņa dizains, ko izmanto augstas frekvences fāzes bloķētai cilpai

- Kešatmiņas un kešatmiņas kontrollera dizains ar VHDL

- ASTRAN balstīta mazjaudas 3-2 un 4-2 papildinātāju kompresoru ieviešana

- Priekšapmaksas elektrības norēķinu sistēma, izmantojot On-Chip dizainu

- Pārklāšanās ieviešana, izmantojot loģisko šūnu un tās jaudas analīzi

- Carry Look Ahead Adder ar dažādu bitu veiktspējas analīzi, izmantojot VHDL

- Datu saites slāņa dizains ar Wi-Fi MAC Protokoli

- FPGA ieviešana savstarpējās autentifikācijas protokolam ar moduļu aritmētiku

- PWM signālu ģenerēšana, izmantojot FPGA un mainīga darba ciklu

Reāllaika projekti

Saraksts VLSI reālā laika projekti galvenokārt ietver VLSI mini projektus, izmantojot VHDL kodu, un VLSI programmatūras projektus ECE inženierzinātņu studentiem.

- SRAM rindas kešatmiņas praktiska integrācija neviendabīgā 3-D DRAM arhitektūrā, izmantojot TSV

- Iebūvēta paštestēšanas metode aizkavētu defektu diagnosticēšanai uz klasteru balstītu lauka programmējamu vārtu masīvos

- ASIC Kompleksā reizinātāja projektēšana

- Zemu izmaksu VLSI ieviešana efektīvai impulsu trokšņu noņemšanai

- FPGA pamatā Kosmosa vektora PWM Trīsfāžu indukcijas motora piedziņas vadības IC

- VLSI automātiskā korelatora un CORDIC algoritma ieviešana OFDM balstītam WLAN

- Automātiska ceļa ieguve, izmantojot augstas izšķirtspējas satelītattēlus

- VHDL dizains attēlu segmentēšanai, izmantojot Gabora filtru slimību noteikšanai

- Zemas sarežģītības pakāpes turbodekoderu arhitektūra energoefektīviem bezvadu sensoru tīkliem

- Ortogonālā koda pārveidošanas iespēju uzlabošana, izmantojot FPGA ieviešanu

- Peldošā punkta ALU projektēšana un ieviešana

- CORDIC dizains fiksētam rotācijas leņķim

- Produktu Reed-Solomon kodi NAND zibspuldzes kontrollera ieviešanai FPGA mikroshēmā

- Statistiskā SRAM lasīšanas piekļuves ienesīguma uzlabošana, izmantojot negatīvās kapacitātes ķēdes

- MIMO tīkla saskarņu enerģijas pārvaldība mobilajās sistēmās

- Datu šifrēšanas standarta datu šifrēšana

- Mazjaudas un platības ziņā efektīvs pārvadāšanas atlases papildinātājs

- UART sintēze un ieviešana, izmantojot VHDL kodus

- Uzlabotas sakausēta peldošā komata pievienošanas un atņemšanas vienības arhitektūra

- FPGA bāzes 1-bitu pilnciparu raidītājs, kas izmanto Delta-Sigma modulāciju ar RF izeju SDR

- Ķēdes meklēšanas izmantošanas optimizēšana BCH dekoderī augstas kļūdu līmeņa pārraidei

- Digitālais DS-CDMA raidītāja dizains, izmantojot Verilog HDL un FPGA

- Efektīvas sistoliskās masīva arhitektūras projektēšana un ieviešana

- VLSI balstīts robotu dinamikas mācību algoritms

- Daudzpusīgs multimediju funkcionālo vienību dizains, izmantojot viltus enerģijas nomākšanas tehniku

- Autobusu tilta projektēšana starp AHB un OCP

- Asinhrono ķēžu uzvedības sintēze

- Ātruma optimizācija modificētam Viterbi dekoderim, kura pamatā ir FPGA

- I2C saskarnes ieviešana

- Ātrgaitas / mazjaudas reizinātājs, izmantojot uzlabotu viltus enerģijas nomākšanas tehniku

- Virspiegādes ķēžu virtuālā barošanas sprieguma fiksēšana aktīvas noplūdes samazināšanai un vārtu oksīda drošībai

- Uz FPGA balstīts energoefektīvs kanalizators programmatūras definētam radio

- Digitālās fotokameras VLSI arhitektūra un FPGA prototipēšana attēlu drošībai un autentifikācijai

- Iekštelpu robota darbības uzlabošana

- ON-Chip Permutation Network projektēšana un ieviešana daudzprocesoru sistēmai On-Chip

- Simbolu ātruma sinhronizācijas metode mazjaudas bezvadu OFDM sistēmām

- DMA kontrolieris (tieša piekļuve atmiņai), izmantojot VHDL / VLSI

- Pārkonfigurējams FFT, izmantojot CORDIC balstītu arhitektūru MIMI-OFDM uztvērējiem

- Maldinoša strāvas slāpēšanas tehnika multivides / DSP lietojumprogrammām

- BCH kodu efektivitāte digitālo attēlu ūdenszīmēs

- Dual Data Rate SD-RAM kontrolieris

- Gabora filtra ieviešana pirkstu nospiedumu atpazīšanai, izmantojot Verilog HDL

- Praktiskas nanometra skalas noformēšana, izmantojot Aware Standard Cell Library, lai uzlabotu lieko, izmantojot 1 ievietošanas ātrumu

- Bezzudumu datu saspiešanas un dekompresijas algoritms un tā aparatūras arhitektūra

- Sistēma daudzbitu mīksto kļūdu labošanai

- Efektīva testa datu saspiešana uz Viterbi bāzes

- OFDM FFT / IFFT bloku ieviešana

- Attēlu saspiešana uz viļņa bāzes, izmantojot VLSI progresīvo kodēšanu

- VLSI Pipelined Multiplier Less 2d DCT / IDCT arhitektūras ieviešana JPEG

- FPGA balstīta sinhrono secīgo ķēžu kļūmju atdarināšana

Tādējādi tas viss attiecas uz VLSI inženierzinātņu, M.Tech studentu sarakstu, kuri ir noderīgi, izvēloties viņu pēdējā gada projekta tēmu. Pēc dārgā laika pavadīšanas, apskatot šo sarakstu, mēs uzskatām, ka jums ir diezgan laba ideja izvēlēties izvēlēto projekta tēmu no VLSI projektu saraksta un ceram, ka jums ir pietiekami daudz pārliecības, lai pārņemtu jebkuru tēmu no saraksta. sarakstā. Lai iegūtu sīkāku informāciju un palīdzību saistībā ar šiem projektiem, varat rakstīt mums zemāk sniegtajā komentāru sadaļā. Šeit ir jautājums jums, kas ir VHDL?

Fotoattēlu kredīts

- VLSI projekti set-tech