The lauka tranzistors (FET) ir elektroniska ierīce, kurā elektriskais lauks tiek izmantots strāvas plūsmas regulēšanai. Lai to īstenotu, ierīces vārtu un avotu spailēm tiek piemērota potenciāla starpība, kas maina vadītspēju starp drenāžas un avota spailēm, izraisot kontrolētu strāvu, kas plūst pāri šiem spailēm.

Tiek saukti FET vienpolāri tranzistori jo tie ir paredzēti darbam kā viena nesēja tipa ierīces. Jūs atradīsit pieejamus dažāda veida lauka tranzistorus.

Simbols

N-kanālu un p-kanālu JFET grafiskos simbolus var vizualizēt šādos attēlos.

Jūs varat skaidri pamanīt, ka bultiņas, kas norāda uz iekšu, lai n-kanālu ierīce norādītu virzienu, kurā esG(vārtu strāva) ir paredzēts plūst, kad p-n krustojums bija tendenciozs uz priekšu.

P-kanāla ierīces gadījumā apstākļi ir identiski, izņemot bultiņas simbola virziena atšķirību.

Starpība starp FET un BJT

Lauka efekta tranzistors (FET) ir trīs termināļu ierīce, kas paredzēta plaša spektra ķēdes pielietojumiem, kas lielā mērā papildina BJT tranzistora ierīces.

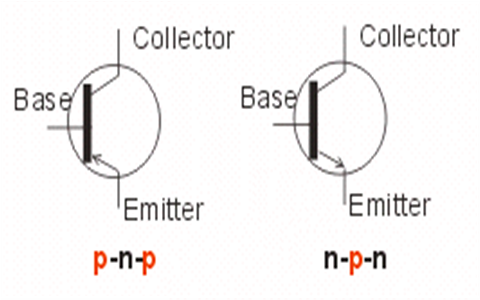

Lai gan jūs atradīsit ievērojamas atšķirības starp BJT un JFET, faktiski ir vairākas atbilstības pazīmes, par kurām tiks runāts nākamajās diskusijās. Galvenā atšķirība starp šīm ierīcēm ir BJT ir strāvas kontrolēta ierīce, kā parādīts 5.1.a attēlā, savukārt JFET tranzistors ir ar spriegumu kontrolēta ierīce, kā norādīts 5.1b.

Vienkārši sakot, pašreizējais esC5.1a attēlā ir tūlītēja I līmeņa funkcijaB. FET strāva I ir sprieguma V funkcijaGSievadīts ieejas ķēdei, kā parādīts 5.1b. attēlā.

Abos gadījumos izejas ķēdes strāvu regulēs ievades ķēdes parametrs. Vienā situācijā strāvas līmenis un otrā - pielietotais spriegums.

Tāpat kā npn un pnp bipolāriem tranzistoriem, jūs atradīsit n-kanālu un p-kanālu lauka tranzistorus. Bet jums jāatceras, ka BJT tranzistors ir bipolāra ierīce, kuras prefikss bi- norāda, ka vadītspējas līmenis ir divu lādiņu nesēju, elektronu un caurumu funkcija.

No otras puses, FET ir a vienpola ierīce tas ir atkarīgs tikai no elektrona (n-kanāla) vai cauruma (p-kanāla) vadītspējas.

Frāzi “lauka efekts” var izskaidrot šādi: mēs visi apzināmies pastāvīgā magnēta spēku piesaistīt metāla vīles magnēta virzienā bez jebkāda fiziska kontakta. Diezgan līdzīgi FET iekšienē elektrisko lauku rada esošie lādiņi, kas ietekmē izejas ķēdes vadīšanas ceļu, bez tieša kontakta starp kontrolējamo un kontrolēto lielumu. Iespējams, ka viena no vissvarīgākajām FET iezīmēm ir tā lielā ieejas pretestība.

Sākot no 1 līdz daudziem simtiem megohmu, tas ievērojami pārsniedz BJT konfigurācijas normālos ieejas pretestības diapazonus, kas ir ārkārtīgi svarīgs atribūts, vienlaikus izstrādājot lineāro maiņstrāvas pastiprinātāju modeļus.

Tomēr BJT ir lielāka jutība pret ievades signāla izmaiņām. Tas nozīmē, ka izejas strāvas izmaiņas BJT parasti ir ievērojami lielākas nekā FET attiecībā uz tādu pašu izmaiņu viņu ieejas spriegumā.

Tādēļ BJT pastiprinātāju maiņstrāvas sprieguma pieaugums var būt daudz lielāks, salīdzinot ar FET.

Vispārīgi runājot, FET ir termiski izturīgāki nekā BJT, kā arī bieži ir mazāki pēc struktūras, salīdzinot ar BJT, kas padara tos īpaši piemērotus iebūvēšanai kā integrālās shēmas (IC)mikroshēmas.

Savukārt dažu FET strukturālās īpašības var ļaut viņiem būt īpaši jutīgiem pret fiziskiem kontaktiem nekā BJT.

Vairāk BJT / JFET attiecību

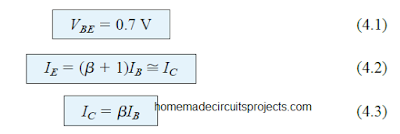

- Par BJT VBE= 0,7 V ir svarīgs faktors, lai sāktu tā konfigurācijas analīzi.

- Līdzīgi parametrs IG= 0 A parasti ir pirmā lieta, kas tiek apsvērta JFET ķēdes analīzē.

- BJT konfigurācijai esBbieži ir pirmais faktors, kas jānosaka.

- Tāpat arī JFET parasti tas ir VGS.

Šajā rakstā mēs pievērsīsimies JFET vai savienojuma lauka efekta tranzistoriem, nākamajā rakstā mēs runāsim par metāla oksīda-pusvadītāju lauka efceta tranzistoru vai MOS-FET.

JFETU BŪVNIECĪBA UN RAKSTUROJUMS

Kā mēs uzzinājām earliet, JFET ir 3 vadītāji. Viens no tiem kontrolē pašreizējo plūsmu starp pārējiem diviem.

Tāpat kā BJT, arī JFET ierīcēs n-kanālu ierīce tiek izmantota redzamāk nekā p-kanālu kolēģi, jo n ierīces mēdz būt efektīvākas un lietotājam draudzīgākas, salīdzinot ar p-ierīci.

Nākamajā attēlā mēs varam redzēt n-kanālu JFET pamatstruktūru vai uzbūvi. Mēs varam redzēt, ka n veida kompozīcija veido galveno kanālu pāri p veida slāņiem.

N-veida kanāla augšdaļa ir savienota, izmantojot Ohmic kontaktu ar termnalu, ko sauc par drenāžu (D), savukārt tā paša kanāla apakšējā daļa ir savienota arī caur Ohmic kontaktu ar citu termināli ar nosaukumu Avots (S).

Pāris p-veida materiāli kopā ir savienoti ar termināli, ko dēvē par vārtiem (G). Būtībā mēs atklājam, ka kanalizācijas un avota spailes ir savienotas ar n-veida kanāla galiem. Vārtu spaile ir savienota ar p-kanālu materiāla pāri.

Ja pāri jfetam netiek piemērots spriegums, tā diviem p-n savienojumiem nav nekādu novirzes apstākļu. Šajā situācijā katrā krustojumā pastāv izsīkšanas reģions, kā norādīts iepriekš redzamajā attēlā, un tas izskatās diezgan kā diodes p-n reģions bez nekādas novirzes.

Ūdens analoģija

JFET darba un vadības darbības var saprast, izmantojot šādu ūdens analoģiju.

Šeit ūdens spiedienu var salīdzināt ar pielietoto sprieguma lielumu no notekas līdz avotam.

Ūdens plūsmu var salīdzināt ar elektronu plūsmu. Krāna mute atdarina JFET avota spaili, savukārt krāna augšējā daļa, kur ūdens tiek iespiests, attēlo JFET noteku.

Krāna poga darbojas kā JFET vārti. Ar ieejas potenciāla palīdzību tā kontrolē elektronu plūsmu (lādiņu) no notekas līdz avotam, tāpat kā krāna poga kontrolē ūdens plūsmu uz mutes atveres.

No JFET struktūras mēs varam redzēt, ka notekas un avota spailes atrodas n-kanāla pretējos galos, un, tā kā termins ir balstīts uz elektronu plūsmu, mēs varam rakstīt:

VGS= 0 V, VDSZināma pozitīva vērtība

5.4. Attēlā mēs varam redzēt pozitīvu spriegumu VDSlietots visā n kanālā. Vārtu terminālis ir tieši savienots ar avotu, lai izveidotu nosacījumu VGS= 0V. Tas ļauj vārtiem un avota spailēm atrasties identiskā potenciālā, kā rezultātā katra p-materiāla apakšējā gala iztukšošanas apgabals ir tieši tāds, kādu mēs redzam pirmajā diagrammā ar neobjektivitātes nosacījumu.

Tiklīdz spriegums VDD(= VDS), elektronus velk uz drenāžas spaili, radot parasto strāvas ID plūsmu, kā norādīts 5.4. attēlā.

Lādiņa plūsmas virziens atklāj, ka notekas un avota strāva ir vienāda pēc lieluma (ID= EsS). Saskaņā ar apstākļiem, kas attēloti 5.4. Attēlā, lādiņa plūsma izskatās diezgan neierobežota, un to ietekmē tikai n-kanāla pretestība starp noteku un avotu.

Jūs varat novērot, ka iztukšošanas reģions ir lielāks ap abu p veida materiālu augšējo daļu. Šī reģiona lieluma atšķirība ir ideāli izskaidrojama ar 5.5. Iedomāsimies, ka n kanālā ir vienāda pretestība, un to varētu sadalīt līdz sekcijām, kas norādītas 5.5. Attēlā.

Pašreizējā esDvar izveidot sprieguma diapazonus caur kanālu, kā norādīts tajā pašā attēlā. Rezultātā p-veida materiāla augšējais reģions tiks apgriezts pretēji ar līmeni aptuveni 1,5 V, apakšējam apgabalam tikai par 0,5 V.

Punkts, ka p-n krustojums ir apgriezts pret visu kanālu, rada vārtu strāvu ar nulles ampēriem, kā parādīts tajā pašā attēlā. Šī īpašība, kas noved pie IG= 0 A ir svarīga JFET īpašība.

Kā VDSpotenciāls tiek palielināts no 0 līdz dažiem voltiem, strāva palielinās saskaņā ar Ohma likumu un I diagrammuD5. rindiņaDSvar izskatīties kā pierādīts 5.6. attēlā.

Diagrammas salīdzinošais taisnums parāda, ka V zemas vērtības reģioniemDS, pretestība būtībā ir vienāda. Kā VDSpaaugstinās un tuvojas līmenim, kas 5.6. attēlā pazīstams kā VP, noplicināšanas reģioni paplašinās, kā norādīts 5.4. attēlā.

Tā rezultātā acīmredzami samazinās kanāla platums. Samazinātais vadīšanas ceļš noved pie pretestības pieauguma, izraisot 5.6. Att. Līkni.

Jo horizontālāka kļūst līkne, jo lielāka ir pretestība, kas norāda, ka pretestība horizontālajā apgabalā kļūst pret “bezgalīgiem” omiem. Kad VDSpalielinās tādā mērā, ka šķiet, ka abi noplicināšanas reģioni var “saskarties”, kā parādīts 5.7. attēlā, rodas situācija, kas pazīstama kā saspiešana.

Summa, par kuru VDSattīstās šī situācija tiek saukta iekniebt spriegumu, un to simbolizē VPkā parādīts 5.6. attēlā. Kopumā vārds pinch-off ir maldinošs, jo tas nozīmē pašreizējo IDir “saspiests” un nokrītas līdz 0 A. Kā pierādīts 5.6. attēlā, tas šajā gadījumā diez vai izskatās acīmredzami. EsDsaglabā piesātinājuma līmeni, ko raksturo kā IDSS5.6. attēlā.

Patiesība ir tāda, ka turpina pastāvēt ļoti mazs kanāls, kura strāva ir ievērojami augsta.

Punkts, kurā ID neizkrīt iekniebt un saglabā piesātinājuma līmeni, kā norādīts 5.6. attēlā, apstiprina ar šādu pierādījumu:

Tā kā nav iztukšošanas strāvas, tiek novērsta dažādu potenciālo līmeņu iespējamība, izmantojot n-kanālu materiālu, lai noteiktu mainīgo pretējā slīpuma daudzumu gar p-n krustojumu. Rezultāts ir izsīkuma reģiona sadalījuma zudums, kas izraisīja iekniebt sākt ar.

Palielinot VDSvirs VP, ciešā kontakta reģions, kurā abi noplicināšanas reģioni saskarsies savā starpā, gar kanālu palielinās. Tomēr ID līmenis joprojām nemainās.

Tādējādi brīdis VDSir augstāks par Vlpp, JFET iegūst pašreizējā avota īpašības.

Kā pierādīts 5.8. Attēlā, strāvu JFET nosaka pie ID= EsDSS, bet spriegums VDSaugstāku par VP nosaka savienotā slodze.

IDSS apzīmējuma izvēle ir balstīta uz faktu, ka strāvai Drain to Source ir īsslēgta saite pāri vārtiem uz avotu.

Turpmāka izpēte dod mums šādu vērtējumu:

EsDSSir vislielākā iztukšošanas strāva JFET, un to nosaka V nosacījumiGS= 0 V un VDS> | VP |

Ievērojiet, ka 5.6. V attēlāGSir 0 V pilnai līknes izstiepšanai. Turpmākajās sadaļās mēs uzzināsim, kā 5.6. Att. Atribūti tiek ietekmēti, kad V līmenisGSir daudzveidīgs.

VGS <0V

Volatage, kas tiek piemērots vārtiem un avotam, tiek apzīmēts kā VGS, kas ir atbildīgs par JFET darbību kontroli.

Ja mēs ņemam BJT piemēru, tāpat kā es līknesCpret VŠOtiek noteikti dažādiem I līmeņiemB, līdzīgi I līknesDpret VDSdažādiem V līmeņiemGSvar izveidot JFET kolēģim.

Šim nolūkam vārtu terminālis ir iestatīts uz zemāku potenciālu zem avota potenciāla līmeņa.

Atsaucoties uz zemāk redzamo 5.9. Attēlu, vārtu / avota spailēm -1 V tiek uzklāts uz samazinātu VDSlīmenī.

Negatīvās iespējamās novirzes mērķis VGSir attīstīt noplicināšanas reģionus, kas līdzinās V situācijaiGS= 0, bet pie ievērojami samazinātas VDS.

Tas liek vārtiem sasniegt piesātinājuma punktu ar zemāku V līmeniDSkā norādīts 5.10. attēlā (VGS= -1 V).

Atbilstošais piesātinājuma līmenis IDvar uzskatīt par samazinātu un faktiski turpina samazināties kā VGStiek padarīts negatīvāks.

5.10. Attēlā jūs varat skaidri redzēt, kā saspiešanas spriegums samazinās ar parabolisku formu kā VGSkļūst arvien negatīvāka.

Visbeidzot, kad VGS= -Vlpp, tas kļūst pietiekami negatīvs, lai noteiktu piesātinājuma līmeni, kas galu galā ir 0 mA. Šajā līmenī JFET ir pilnībā “izslēgts”.

V līmenisGSkas izraisa IDlai sasniegtu 0 mA, raksturo VGS= VPkur VPir negatīvs spriegums n-kanālu ierīcēm un pozitīvs spriegums p-kanālu JFET.

Parasti lielākā daļa JFET datu lapu var parādīties iekniebt spriegums norādīts kā VGS (izslēgts)V vietāP.

Laukums, kas atrodas augšējā attēlā, saspiešanas lokusa labajā pusē, ir vieta, ko parasti izmanto lineārajos pastiprinātājos, lai panāktu traucējumus nesaturošu signālu. Šo reģionu parasti sauc nemainīgas strāvas, piesātinājuma vai lineārās amplifikācijas reģions.

Sprieguma kontrolēts rezistors

Teritoriju, kas atrodas vienā un tajā pašā attēlā saspraužamās lokusa kreisajā pusē, sauc par omas apgabals vai ar spriegumu kontrolēts pretestības reģions.

Šajā reģionā ierīci faktiski var darbināt kā mainīgu rezistoru (piemēram, automātiskā pastiprinājuma kontroles lietojumprogrammā), un tā pretestību kontrolē caur pielietoto vārtu / avota potenciālu.

Var redzēt, ka katras līknes slīpums, kas arī norāda JFET notekas / avota pretestību VDS

Palielinot VGS ar negatīvu potenciālu, katras līknes slīpums kļūst arvien horizontālāks, proporcionāli palielinot pretestības līmeni.

Izmantojot šādu vienādojumu, mēs varam iegūt labu sākotnējo tuvinājumu pretestības līmenim attiecībā pret VGS spriegumu.

p-kanāla JFET darbs

P-kanāla JFET iekšējais izkārtojums un uzbūve ir precīzi identiska n-kanāla kolēģim, izņemot to, ka p- un n-veida materiālu reģioni tiek mainīti otrādi, kā parādīts zemāk:

Strāvas plūsmas virzienus var uzskatīt arī par apgrieztiem, līdz ar faktisko VGS un VDS spriegumu polaritāti. P-kanāla JFET gadījumā kanāls tiks ierobežots, reaģējot uz pozitīva potenciāla palielināšanos pāri vārtiem / avotam.

Apzīmējums ar dubultu indeksu VDSradīs negatīvu spriegumu VDS, kā parādīts 5.12. attēla raksturlielumos. Šeit jūs varat atrast maniDSSpie 6 mA, bet saspiešanas spriegums pie VGS= + 6V.

Lūdzu, nesatraucieties, jo jums ir V mīnus zīmeDS. Tas vienkārši norāda, ka avotam ir lielāks potenciāls nekā kanalizācijai.

Var redzēt, ka līknes augstam VDSlīmenis pēkšņi pieaug līdz vērtībām, kas izskatās neierobežotas. Norādītais vertikālais pieaugums simbolizē sadalīšanās situāciju, kas nozīmē, ka strāvu caur kanāla ierīci šajā laika posmā pilnībā kontrolē ārējā shēma.

Lai gan n-kanālu ierīcei tas nav redzams 5.10. Attēlā, tā var būt iespēja zem pietiekami augsta sprieguma.

Šo reģionu var novērst, ja VDS (maks.)tiek atzīmēts no ierīces datu lapas, un ierīce ir konfigurēta tā, lai faktiskais VDSvērtība ir zemāka par šo atzīmēto vērtību jebkurai VGS.

Pāri: 5 labākās izpētītās 40 vatu pastiprinātāju shēmas Nākamais: 2N3055 datu lapa, Pinout, lietojumprogrammu shēmas